Other Parts Discussed in Thread: TIDA-00364

Hi,

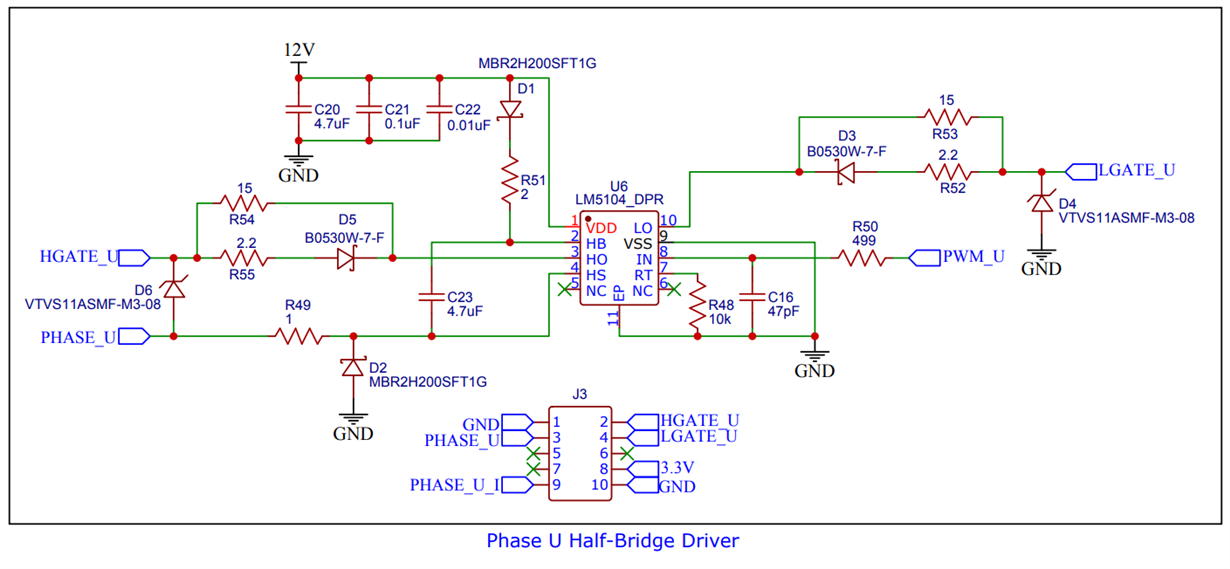

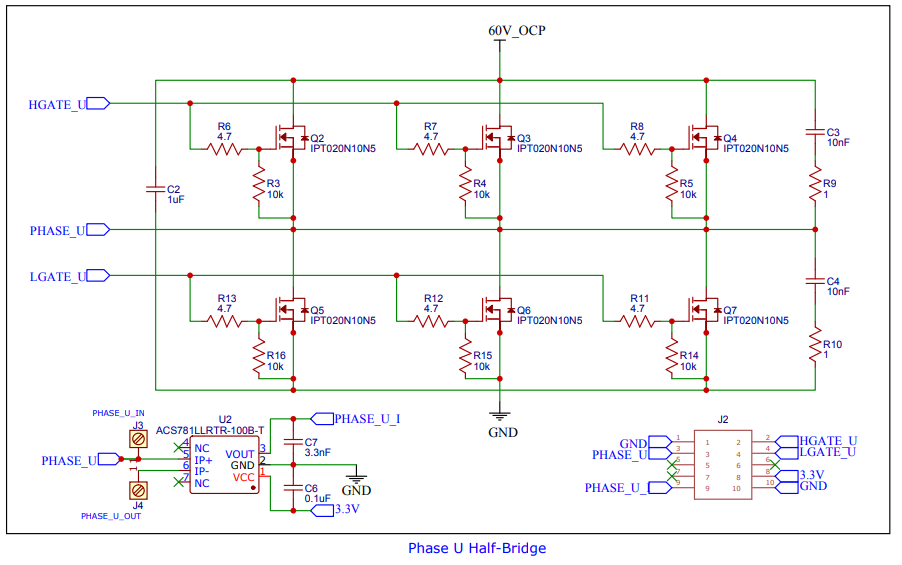

I would like to use three LM5104's to drive mosfets in parallel for a three-phase inverter.

If using individual gate resistors, is it suitable or would there be other precautions. For example is it possible the adaptive delay circuitry would have unintended side effects with parallel mosfets?

Thanks,

Andrew