Other Parts Discussed in Thread: TLV755

Hi All,

I have a strange problem when using the TLV755P as a brownout 3.3V backup supply. Please refer to the schematic below.

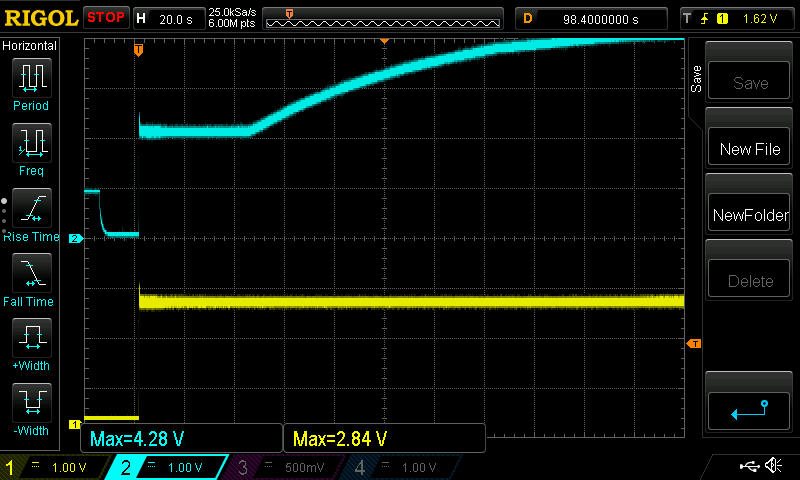

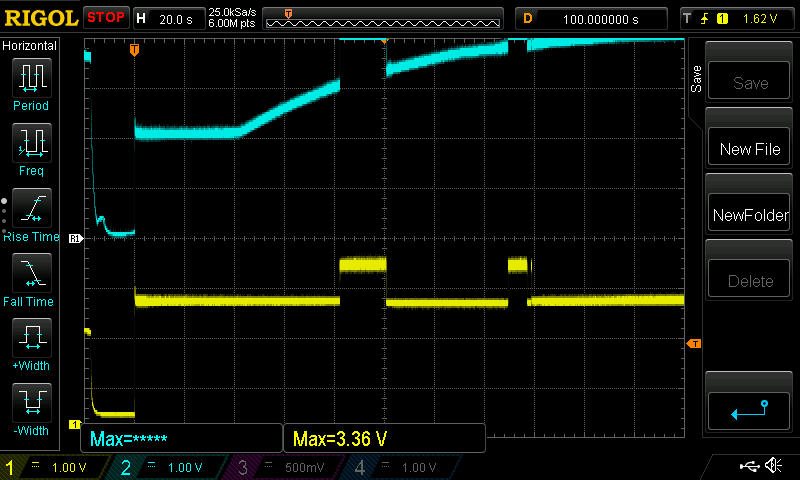

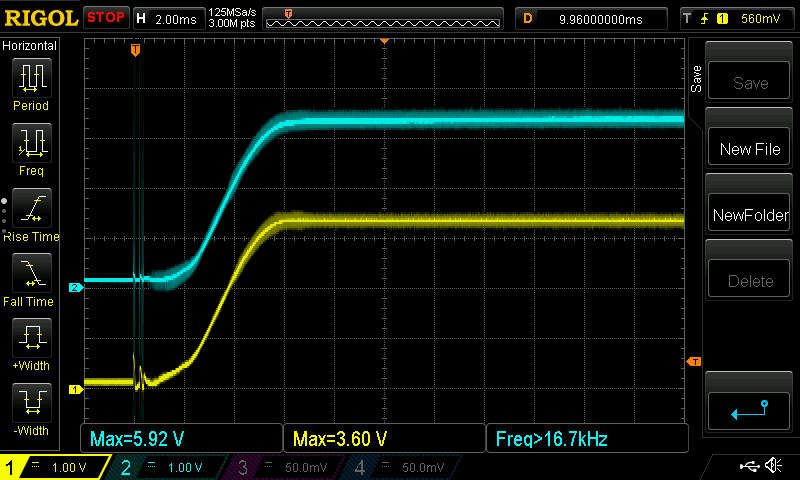

The 3.3V circuit should draw about 100mA in normal operation. The backup circuit is fed from C114 a 5F super cap. To test the circuit, I have disabled the normal 3.3V primary supply. On power-up, the super cap slowly charges from a separate 5V supply to about 4.5V through a super barrier diode D22 in series with R163 a 20R resistor.

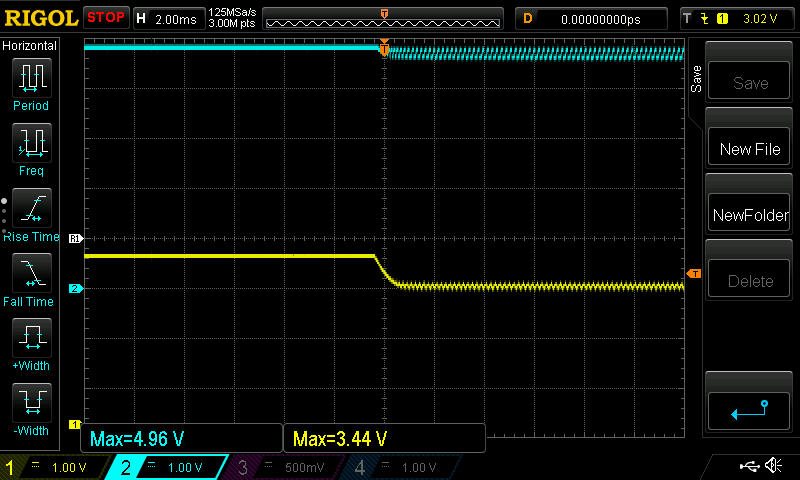

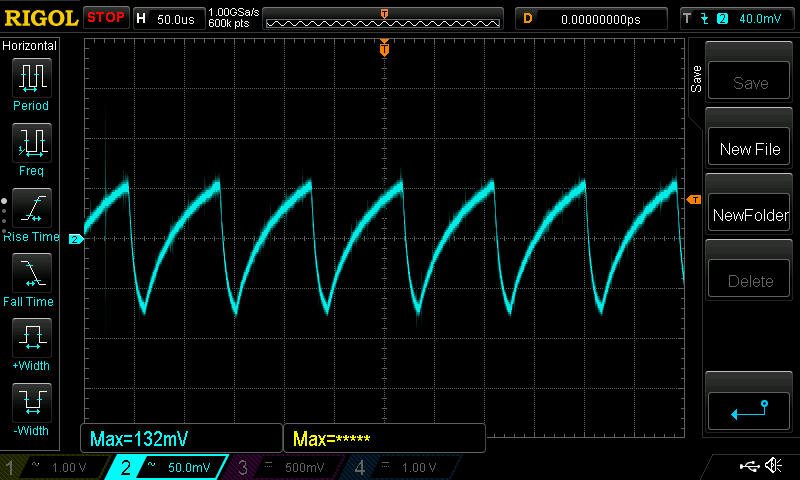

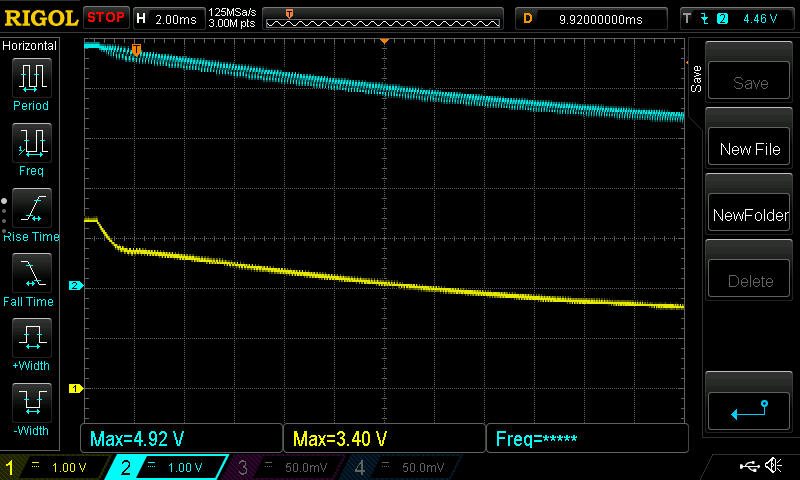

To prevent back feed from the normal 3.35V supply the TLV755P is fed with a second super barrier diode D23 such that Vin is about 4.4V. I have a 10UFD bypass on Vin and 1UFD on Vout right at the chip. When I power up, the output voltage rises to only 2.6V, not 3.3V as it should. At this point, Vin is 4.4V and drawing only a few mA. The device remains cool. If I jumper from 5V directly to Vin the output does go to 3.3V. If I then remove the jumper it immediately drops back to 2.5V again. So, it is not a start-up problem. It does not work if there is even one super barrier diode in the circuit i.e. jumpering D22 or D23 does nothing. I have tried different bypass values and different TLV chips with no effect.

I realize that under full load the 20-ohm resistor would be a problem, dropping 2 volts at 100mA. But remember the super cap will charge all the way to 5V with no backup supply load in normal operation.

Thanks in advance fo any ideas to solve this.