Other Parts Discussed in Thread: BQ76PL455-Q1, BQ76PL455A-Q1, BQ76PL455A

Hello,

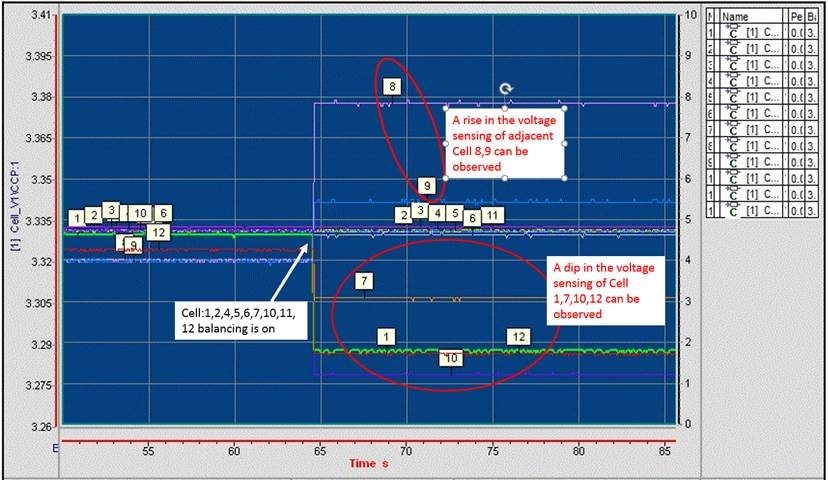

I am doing cell balancing algorithm validation at our company. During the validation, it is observed that there is a instantaneous deep in the cell voltage whose cell balancing is turned ON and there is rise in the cell voltage of the adjacent cells. For e.g. if the balancing of 10th cell is ON there is a dip in the cell 10th voltage and rise in cell 8th and cell 9th voltages. As per the available documents on bq76pl455-q1 slave board, it is specified that there'll be a dip and little rise in the cell voltage, but that is not quantified and the reason is also not given. Need to find the root cause of this issue. Screenshot is attached.

Regards,

Saurabh Shah