Hello experts.

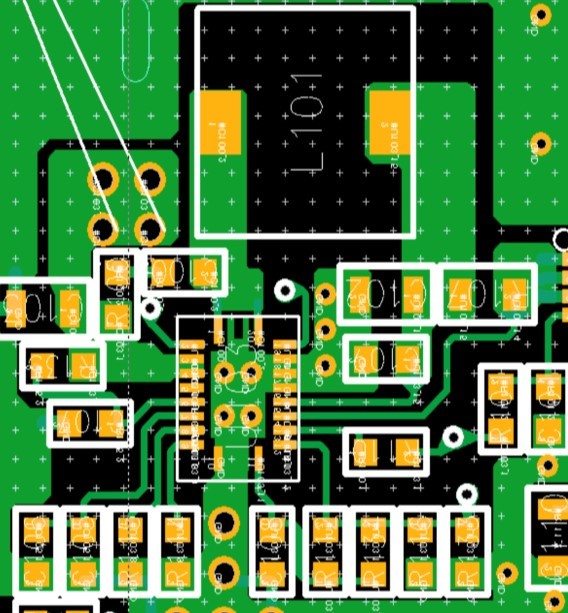

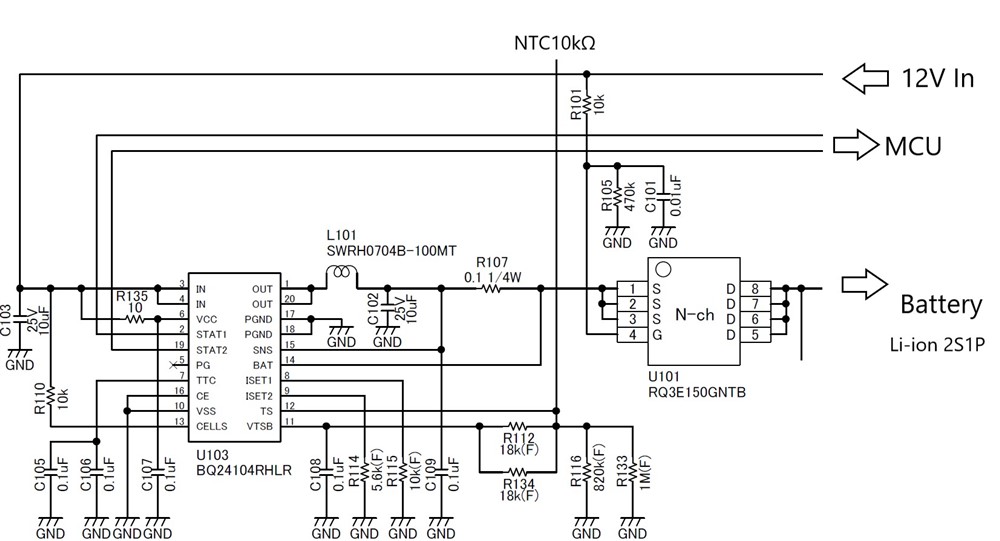

Our battery-pack products have BQ24104 battery charger IC .

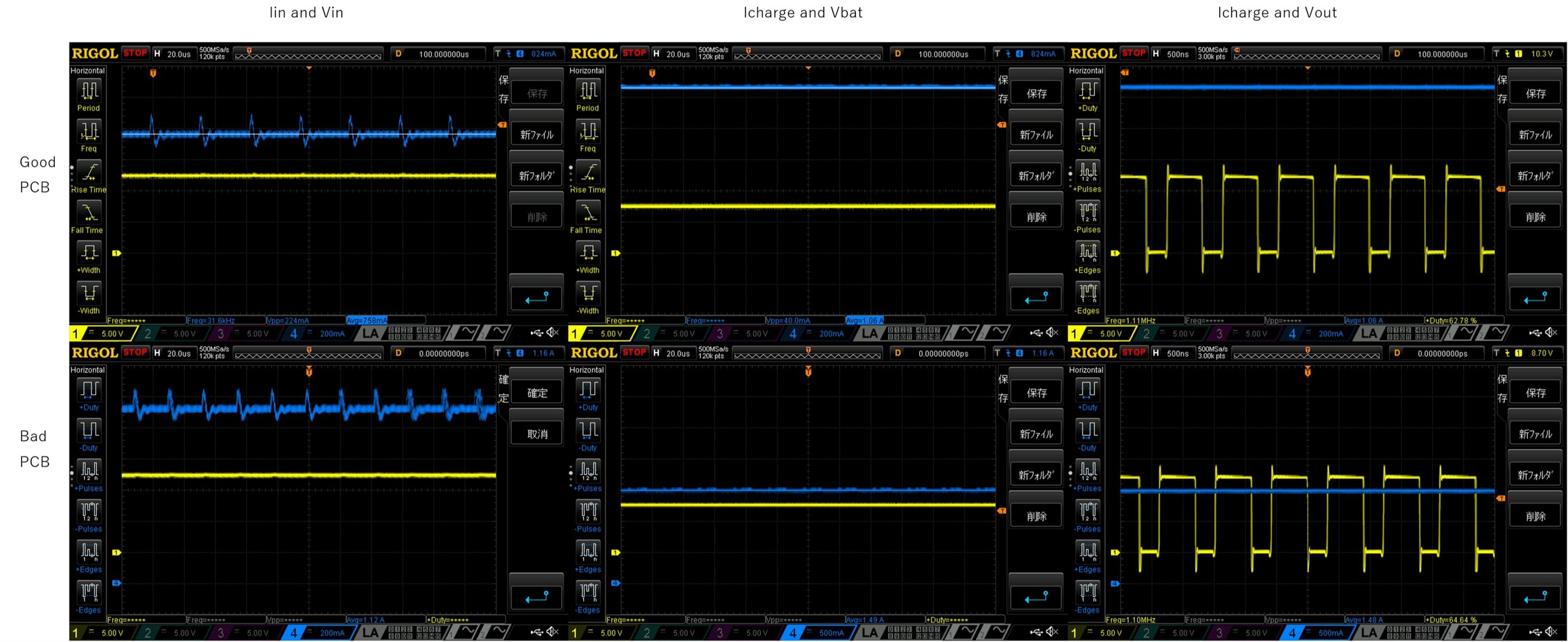

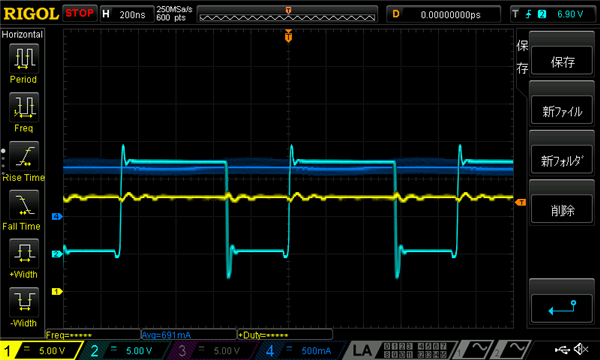

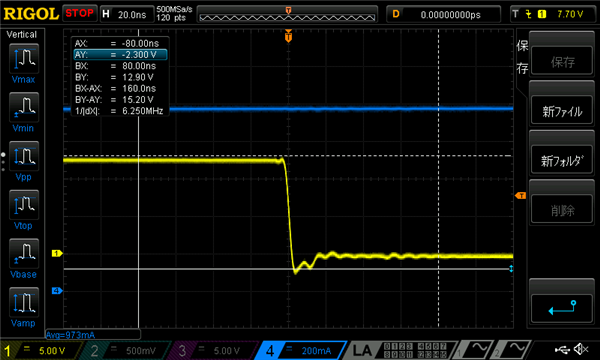

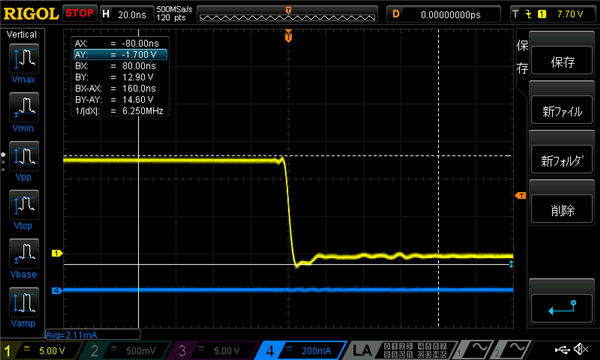

Now there is an overheating problem with BQ24104.

The package surface temperature is more than 90℃ and STAT pins output error.

Not all products have problem, most of them are normal(package temp is around 50℃), but a few products have this problem.

We want to know the cause and countermeasure.

In our circuit, Vin=12V and charge current is about 1A. battery is 2Cell(8.4V) Li-ion.

Our circuit is designed with reference to specsheet Fig16, but there are some differences:

- N-MOS FET between RSNS and BatteryPack+. Gate and Vin, Drain and BatteryPack+, Source and Rsns are connected. FET turns on when 12V input.

- D1 is not mounted

- 10Ω resistor between IN and VCC

- RISET1=10k、RISET2=5.6k

- STAT1/2 are connected to MCU with external PU resistor.

- PG is open