Other Parts Discussed in Thread: IPG-UI, USB2ANY

Dear,

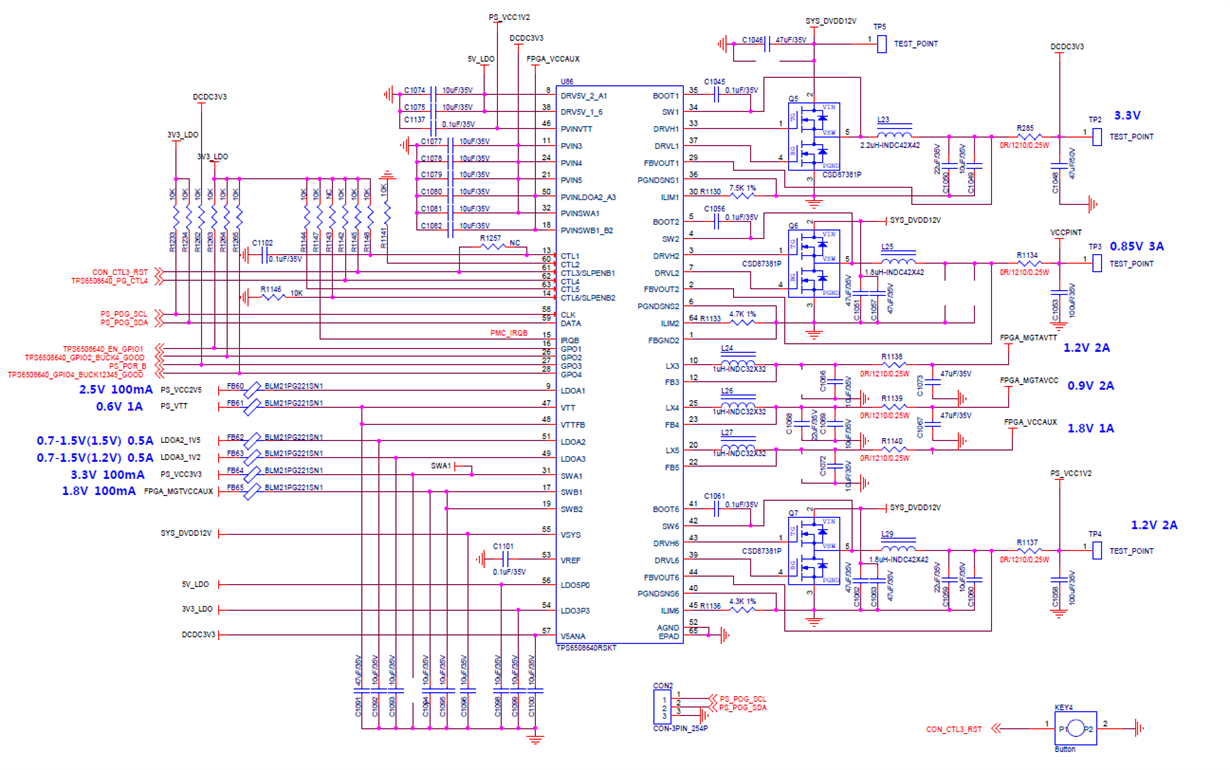

In order to evaluate the TPS6508640RSKT to power the Xilinx MPSoC ZU9, we have designed a power board which only contains TPS6508640RSKT and the required components.

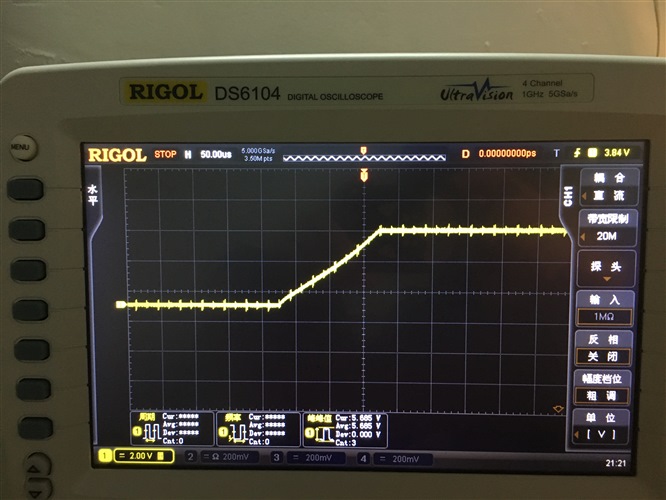

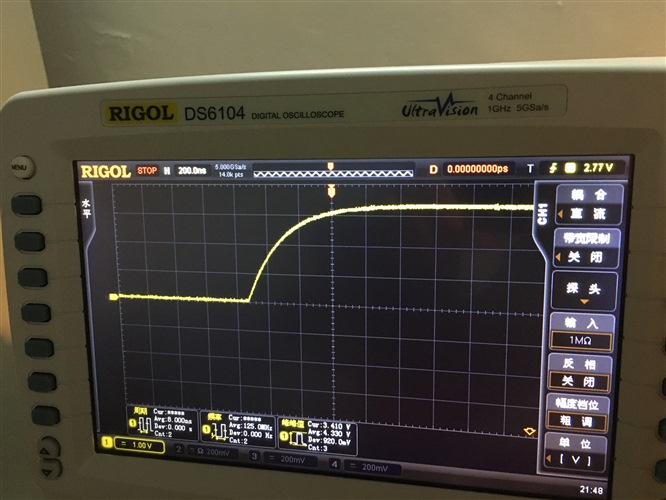

In the initial test, with the input power supply being12V and all the load's being off, we found that LDO5P0 and LDO3P3 do not have output voltage. In my understanding, as long as providing with 12V power, LDO5P0 and LDO3P3 should give the appropriate output voltage. Is my understanding correct? Or any other reason to cause TPS6508640RSKT shutdown?

Thanks ahead.

Regards,