Team,

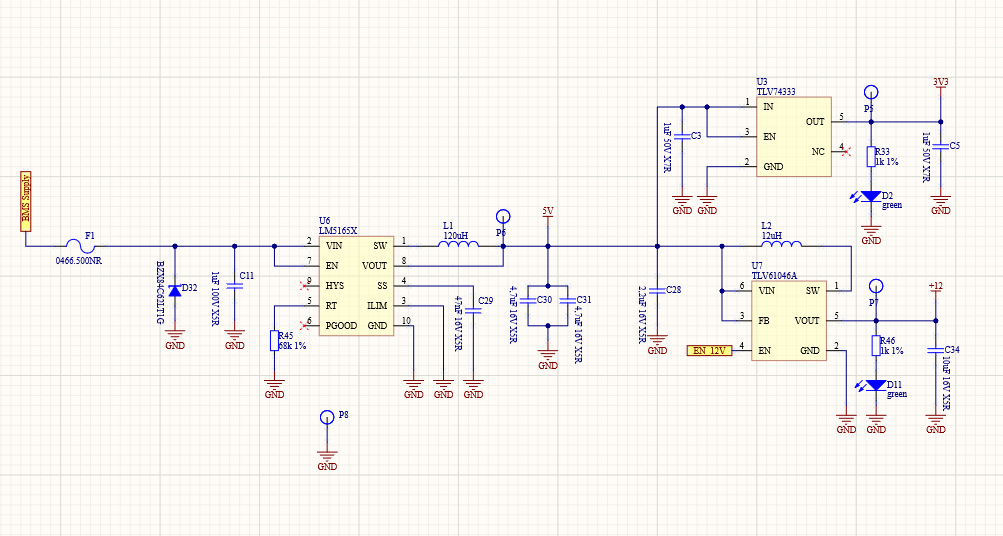

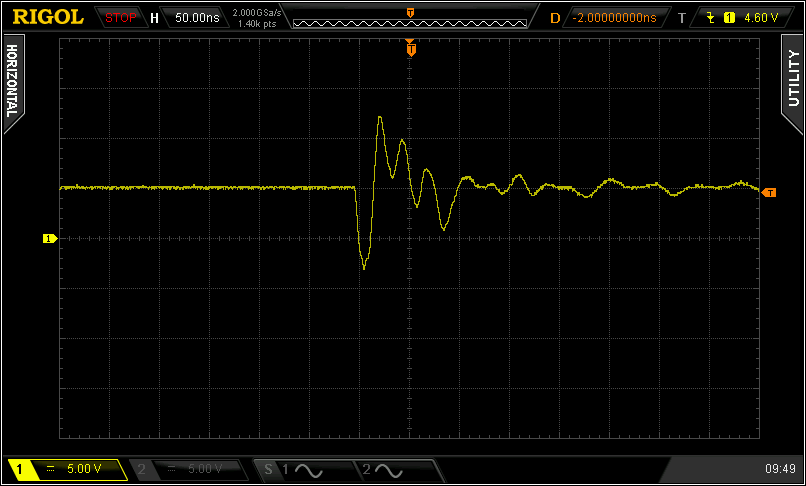

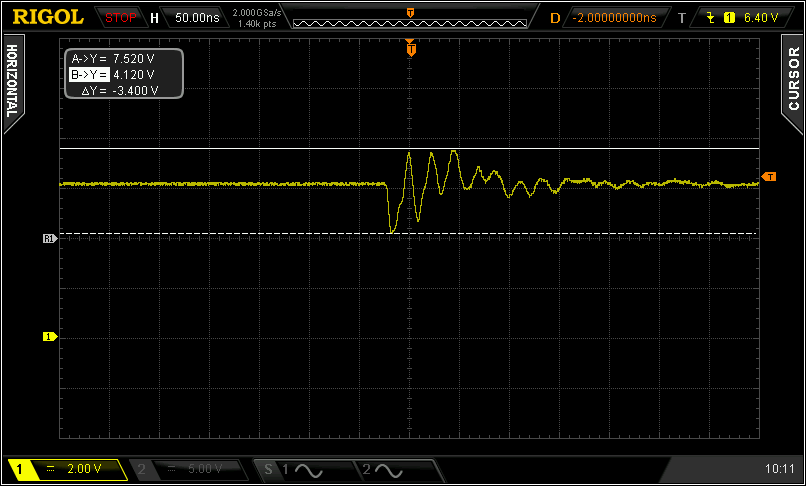

we use LM5165X to convert 48V from battery to 5V, in general it works fine, though when measuring the voltage on the battery with a multimeter, we see a voltage oscillation going to the output of the converter. This oscillation causes a reset of the MCU (5v powered).

What is the best way to address/minimize this oscillation (ferrite bead, additional caps, common mode choke)?

The first scopeshot is when on batt. power, the second on 5V. Oscillation lasts a few tens of nanoseconds, but it's enough for the MCU. Voltage on the battery 41.2V oscillates max to 75.2V and 34V.

Thank you.