I have some questions regarding the internal FET operation of LDO.

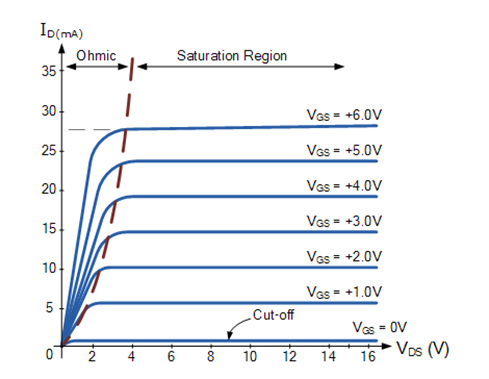

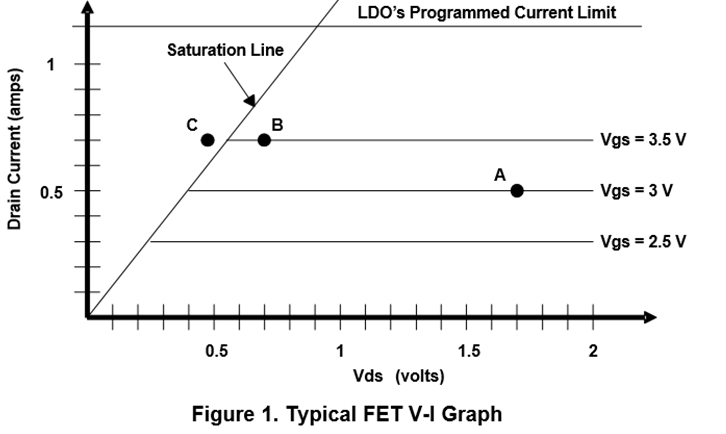

1. In LDO, which uses pass device as FET, Rds(on) is dominated by Vds rather than Vds, Id. Is this right?

2. Assuming Vin=14V, Vout=5V, Iload=100mA, is it Vds=9V and therefore Rds(on)=90ohm?

Assuming Vin=40V, Vout=5V, Iload=100mA, is it Vds=35V and therefore Rds(on)=350ohm?

3. So, is the Vgs adjusted to make Rds(on)=90, 350ohm via feedback?

Does it have to be a specific Vgs to satisfy certain Iload in certain Vds? (and value of Vgs define by FET characteristic)

-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

If above 1~3 is correct,

1. At TSP7b7702 datasheet, max Vdropout at Io=100mA is 500mV which means that Rds(on) is among 5ohm(500mV/100mA) and it seems too big compared to typical low Rds(on) FETs. Can't smaller Rds(on) of FET to lower Vdropout? Why is it used so high?