Other Parts Discussed in Thread: CSD17573Q5B

Hi,

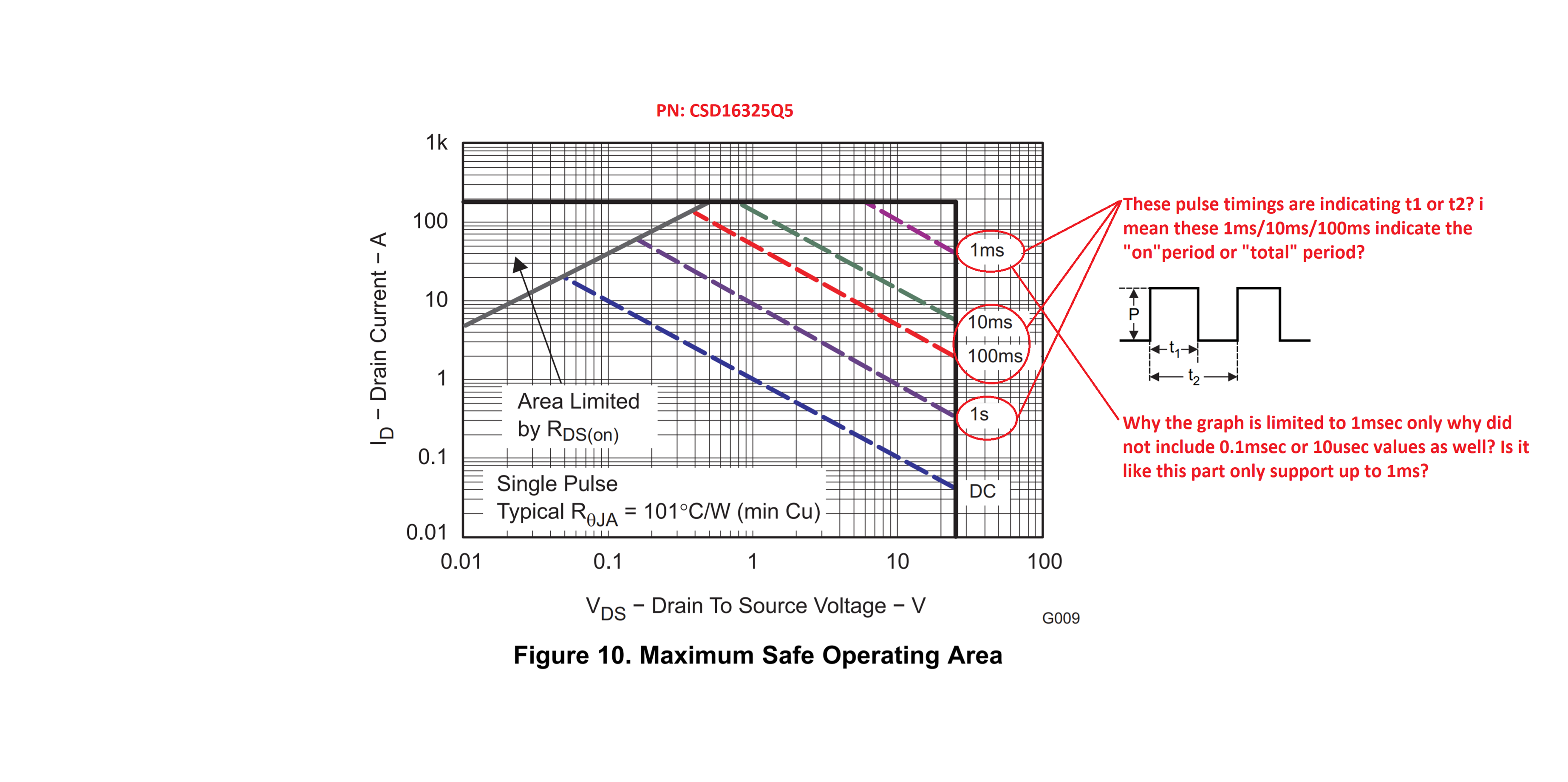

Please see image below, the pulse timings mentioned in the SOA graph, are they the "on" timings of the pulse or "on+off" timings?

I mean if say 1msec means a pulse with 1msec "on" period or a pulse with 1msec of "total" (on+off) period? if 1msec is total period then what is the on period or duty cycle for 1msec? How to understand these numbers?

Also why the graph shows pulse width only up to 1msec why not 100usec or 10usec and further? Does this mean this MOSFET can only support pulses of 1msec not faster/smaller pulse widths than 1msec?

Please suggest

Thanks

Santosh