Hi Don Dapkus,

I read your answer on this thread https://e2e.ti.com/support/power-management/f/196/t/892573?tisearch=e2e-quicksearch when I search for method of calculating mosfet gate drive current.

the two PDF you recommend are very useful, and I have some questions about them.

Q1: In SLUA882, there are Assumptions that " Vgs(miller) ≈ Vgs(th) = 0.5*V_drv,Ig2,3 = 0.5* Ig_peak" in order to simplify the equations to get peak current of gate driver. But I am not very sure whether those assumptions are reasonable or conditionnally reasonable.

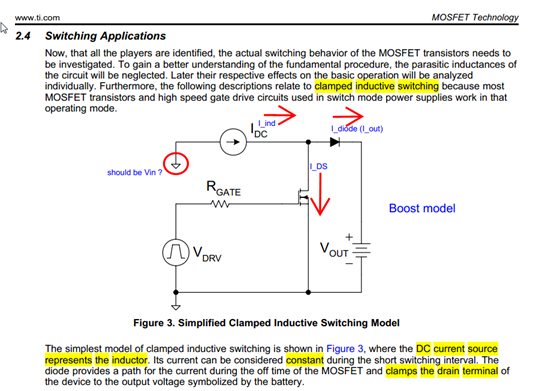

Q2: In slua618a, section 2.4, fig 3, I guess this simplified clamped inductive switching model comes from general BOOST converter topology? If so, I think the left terminal of current soucre IDC (the inductor) should be connected to Vin rather than GND. As I marked red circle below. How do you think ?

Thank you .