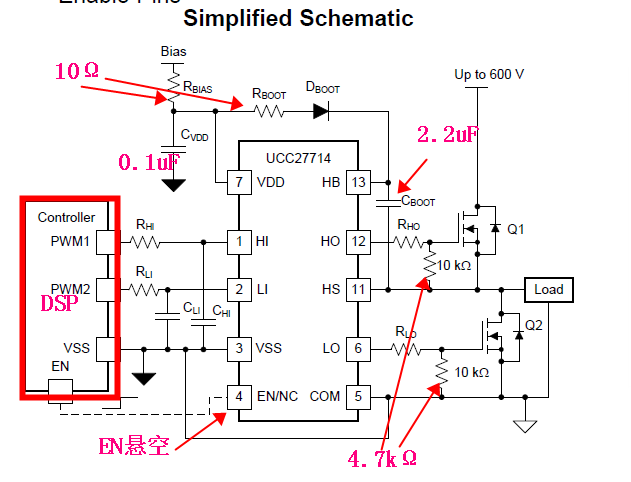

Hi, my customer's schematic is as below(EN floating).

We find that when UCC27714's top temperature reaches 70C, the HB-HS voltage will drop to below 7V, causing UCC27714 to restart repeatedly.

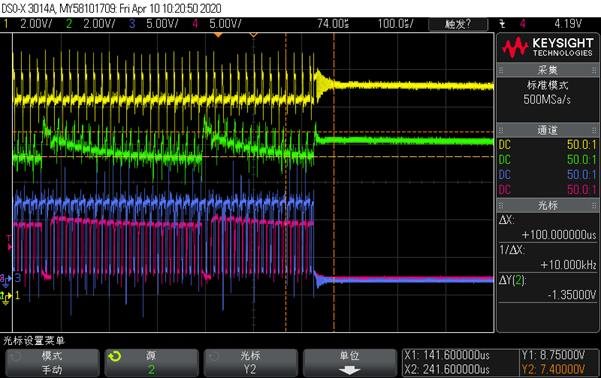

The waveforms are as below:

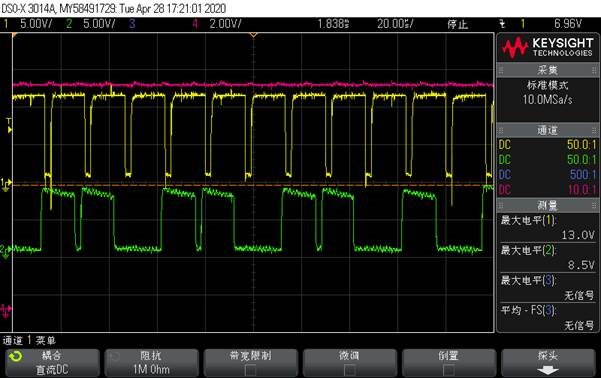

yellow- good bootstrap cap voltage waveform(UCC27714 whose temperature is less than 70C)

blue- good HO-HS voltage waveform

green- bad bootstrap cap voltage waveform(UCC27714 whose temperature is above 70C)

red- bad HO-HS voltage waveform

The device power supply is stable, and we've tried to replace the device and the problem is still there. Within the same device, if we cool down the temperature to below 70C, the problem disappear.

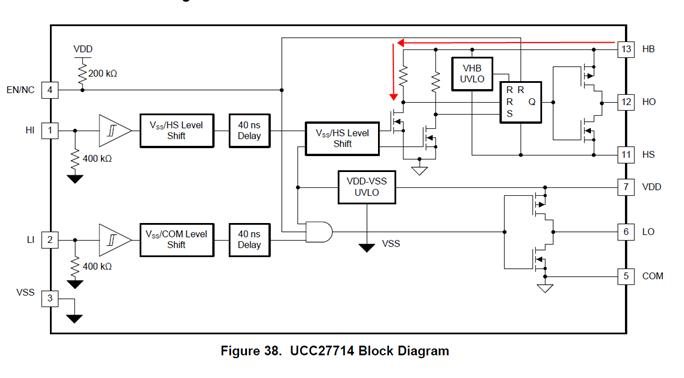

Are there any internal circuit that could discharge the bootstrap capacitor during high temperature? For example the red line shown below?

Are there any risk for the schematic we provide?