Other Parts Discussed in Thread: AM3358, , TPS65218, TPS51200

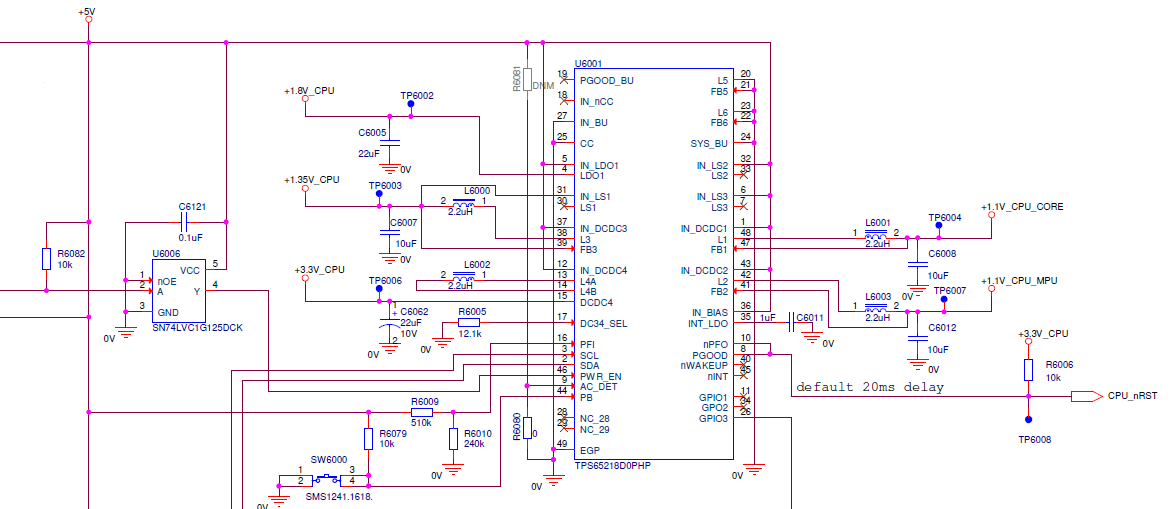

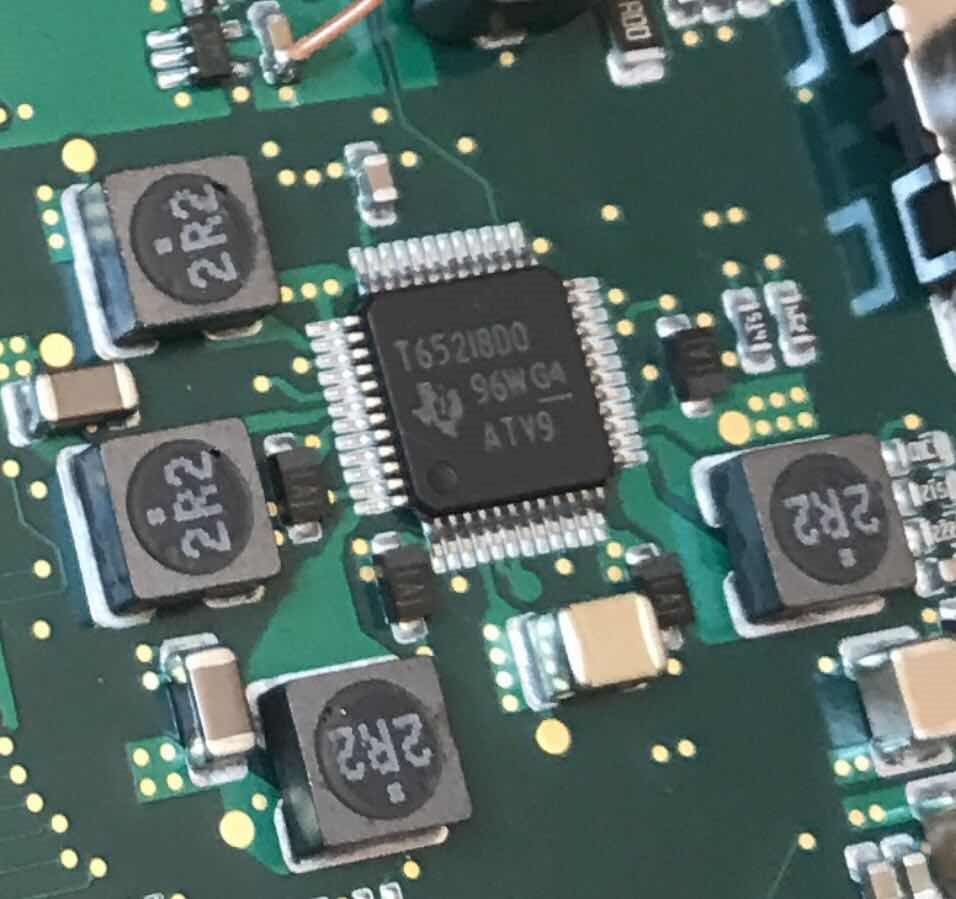

We have an TPS65218D0 connected to an AM3358. The board also has some Cyclone 10 FPGAs connected to other PM parts.

The FPGA I/O (+3.3V) is generated from a LM20143MHE.

The PGOOD signal from that part enables the TPS65218 using pin 46 PWR_EN.

There is thus a power sequence where the FPGA I/O is turned on first.

We have 10 boards. It fails on 9 of them when +3.3V is to turned-on.

The last board we could get to work after changing power supply.

We find that the board draws 0,6A from the 5V.

We have tried with four different power supply on the other boards, but they do not start properly.

We do not use DCDC5 & 6 or GPIO1

We see around 2.2V on the DCDC4, and we suspect that the FPGA I/Os drive the CPU I/Os

It is 3.3-2.2 = 1.1 or almost twopdiode drops.

Schematics below.

The Cap is 22uF, based on http://e2e.ti.com/support/power-management/f/196/t/844935

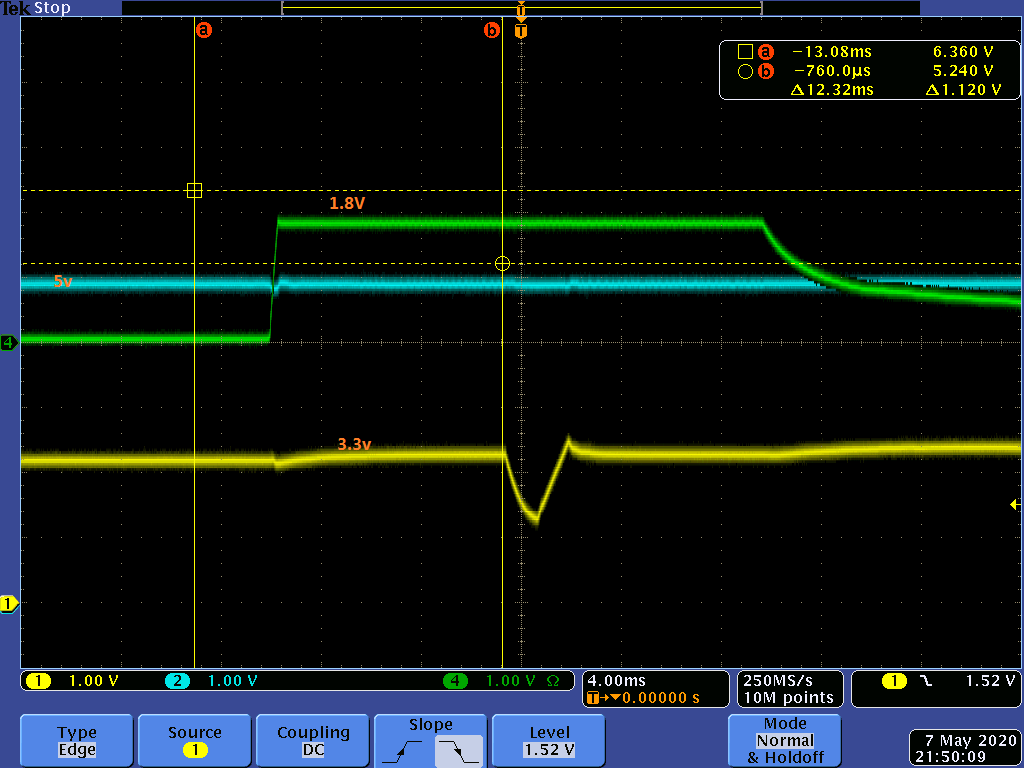

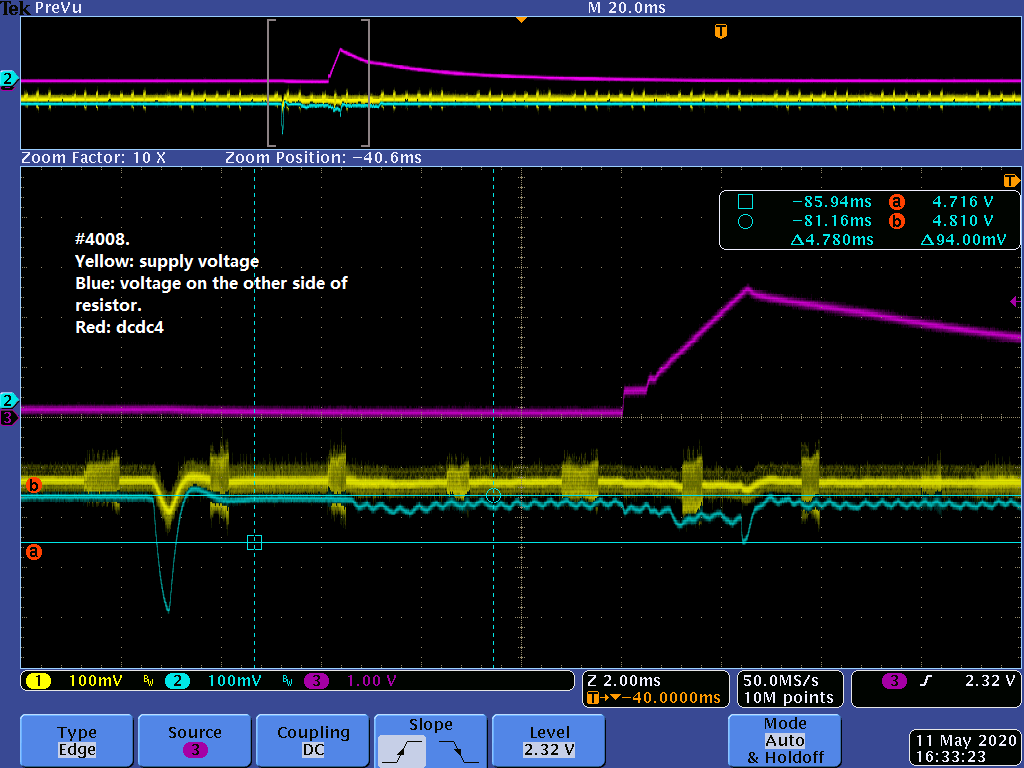

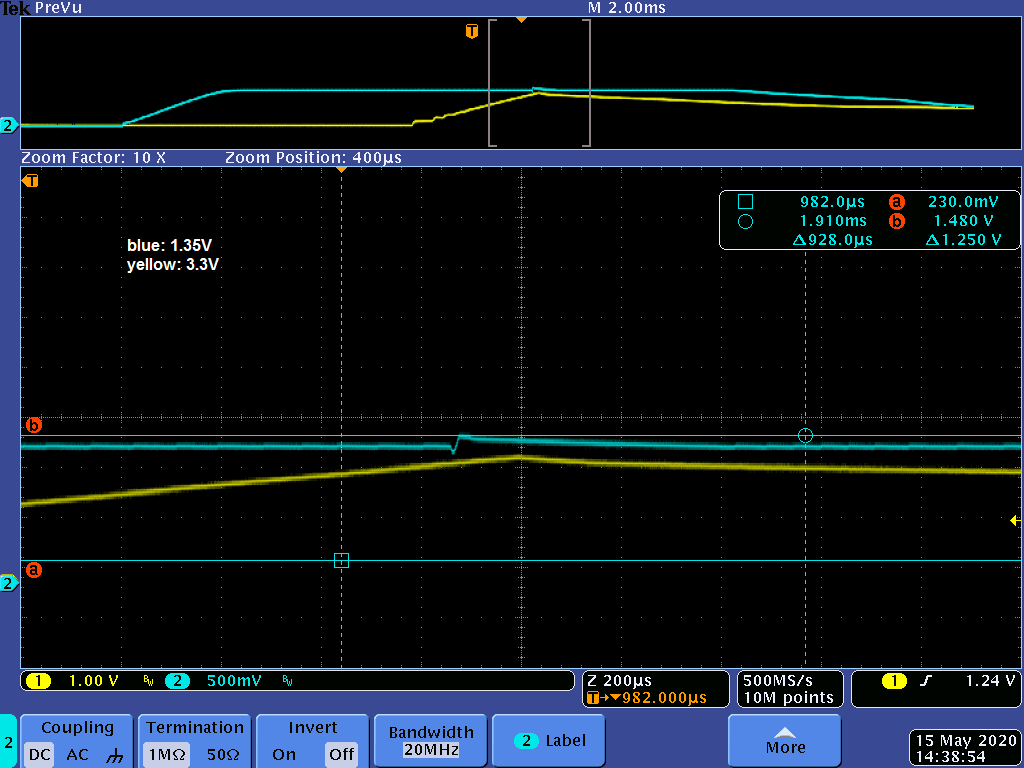

The 1.8V turns on first. There is a minimal dip in the 5V supply when that happens.

Then 1.35V turns on after that. This seems also to work, reaching its voltage in 2 ms.

The 3.3V has ~2.2V value, then starts to *drop* 0.6V, 5 ms after the +1.35V reaches its value, and then starts to increase again

and then shuts off.

We would like to understand the power sequence timing better.

The sequence should be ..., DCDC3=1.35V, GPIO1, DCDC4=+3.3V, ...

DCDC4 (+3.3V) should start DLY5 + DLY6 after DCDC3 (+1.35V)

DLY5 = DLY6 = 2 ms, so DCDC4 should start 4 ms after DCDC3.

In the picture below we see that DCDC4 gets a dip after 7/5*4 ms or 5,6 ms, and then rises to 2.6V until 10/5*4 ms = 8 ms.

This is 2,4 ms after it starts which is before the 5 ms time alloted before it should shut itself down.

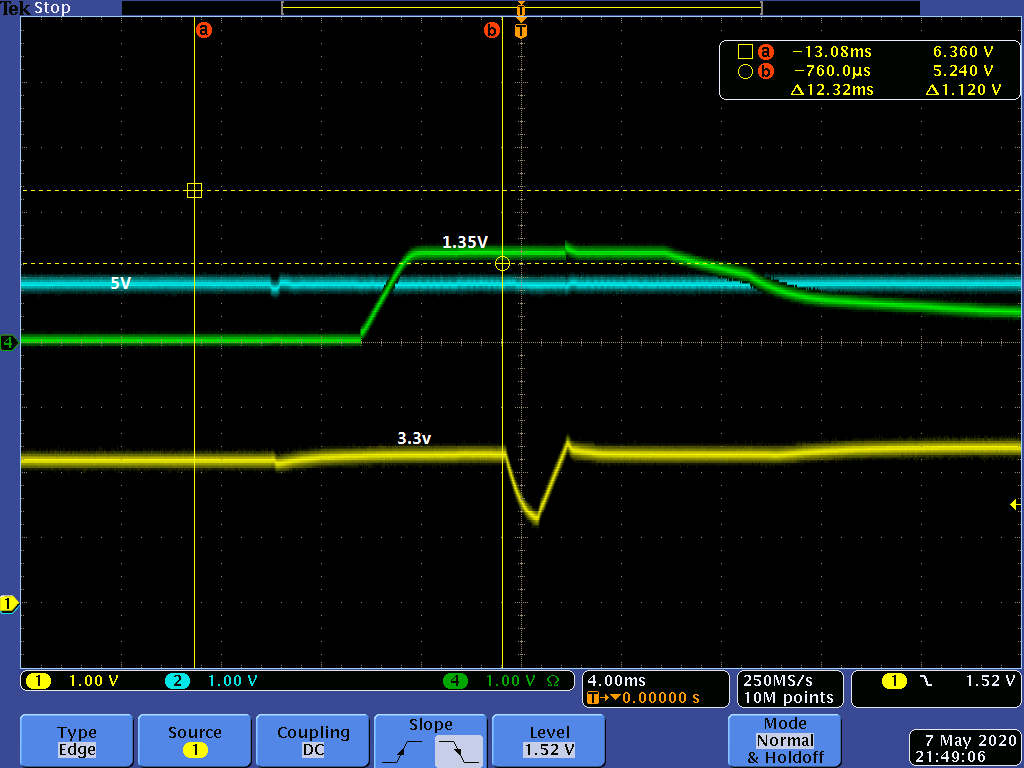

To avoid the interference from the FPGA we shut down the regulator to get this picture.

The +3.3V regulator turns on 7/5*4 ms after the 1.35V, (5,6 ms).

It still shuts down at 10/5 * 4 ms or 8 ms after +1.35V and has reached 2.6V at that time.

We have 15 I/O pins which are pulled up to DCDC4 using 10k ohm resistors.

An LED is connected with a 330 ohm series resistor, but this is normally off in this state.

There is about 60uF of decoupling caps. Most around the CPU (5 x 10uF)

Vcc for

4 x single gate

1 x SPI flash

1 x NAND flash

1 x clock buffer

1 x TPS51200BCT for DDR3 voltage

1 x TMUX1574PW analog mux.

2 x SDRA05-4R2 USB protection circuits.

Does not seem to be something that would overload the DCDC4.

Any ideas?