In a design of ours we have used TPS3780B, to monitor 5V and have found discrepancy in the truth table and the behavior of the IC.

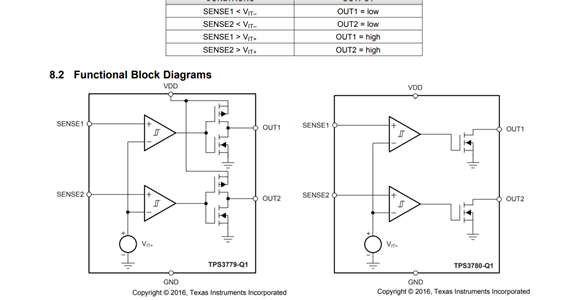

If SENSE1 is greater than the threshold VIT=1.194V, OUT1 = LOW, since output of comparator is high, NMOS will be on, resulting in OUT1 to be logic low.

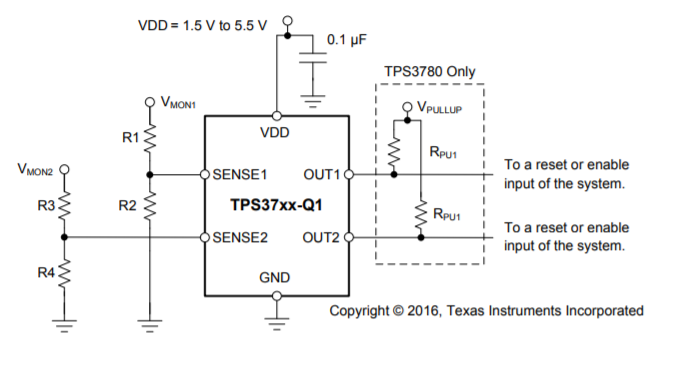

In my design i have used

R1=1.74MΩ and R2=567KΩ so my SENSE1 would be 1.22, greater than 1.194 and OUT1 = LOW

Tried with other values and increased SENSE1 upto 1.8V still OUT1=LOW was the scenario.To see the working when SENSE1<VIT, I have used R1=10MΩ and R2=1MΩ, SENSE1=0.45V, at this condition OUT1 was High.

Please kindly look into the functionality at your end.