Part Number: UCC5390

Hi,

my customer is using UCC5390 to drive SiCFET, there will be very small probability that UCC5390 will output high when input is low, and causing SiCFET false turn on, and they see the requirement below:

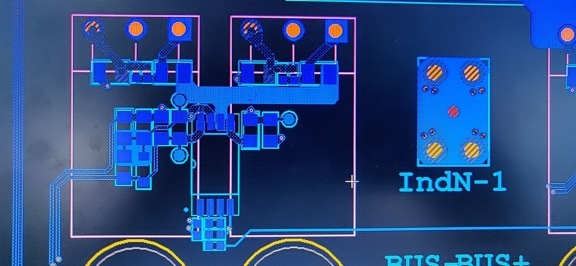

But they haven't followed the requirement, UCC5390 is placed on the first layer shown below:

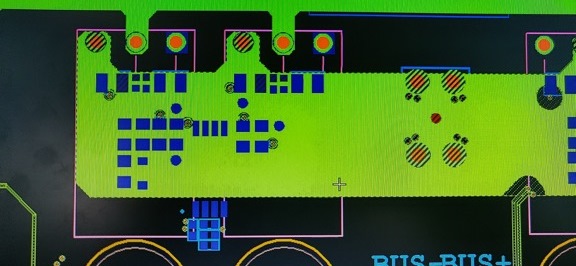

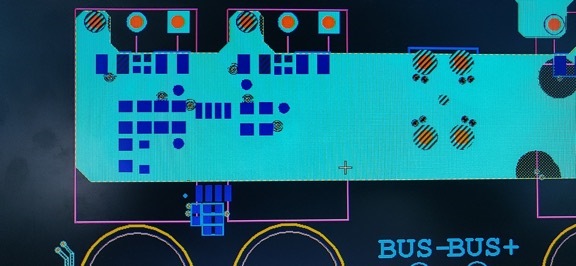

On the third and fourth layer, their will be plane under UCC5390. And there will be current and voltage variation on these 2 planes, dv/dt=43V/ns, di/dt=5A/ns.

They wonder what kind of influence it will bring to the gate driver, may it be the cause of the small probability that UCC5390 that give false high output?

Third layer

Fourth layer