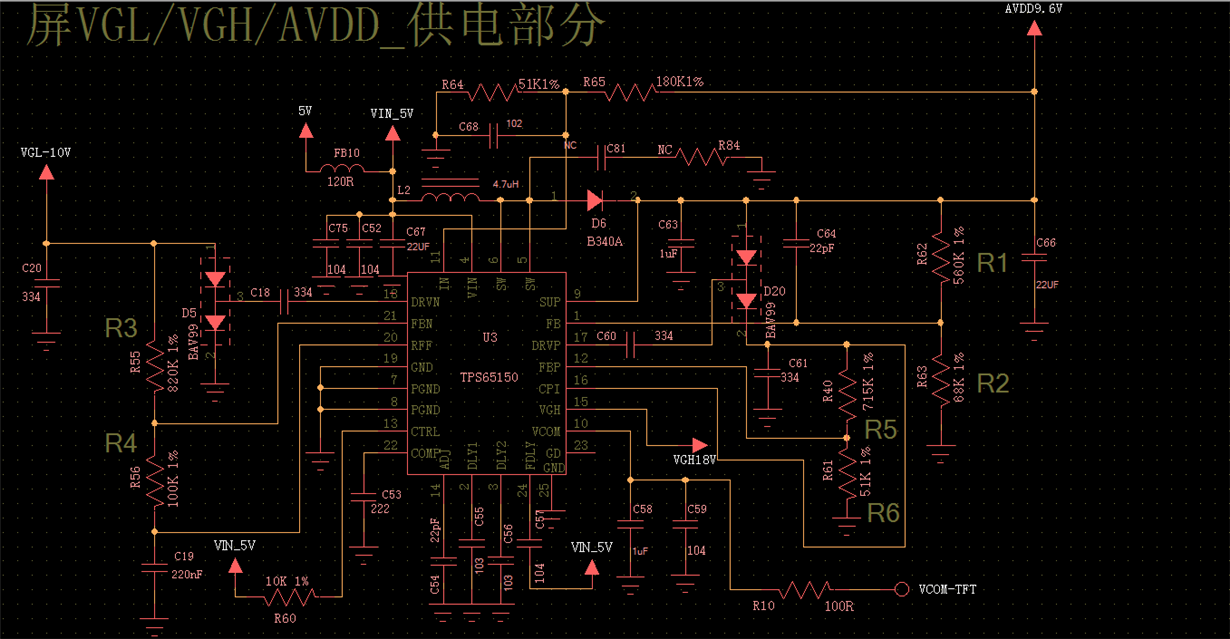

Other Parts Discussed in Thread: TPS65150

HI

Now, tps65150 is used as LCD driver's high and low voltage. It needs + 18V and - 9.6V high and low voltage. In the following two problems (refer to the design below), please provide technical support. Thank you!

1. At the moment of power on (about 40ms), there is a normal switching frequency, and then there is no switching frequency, vs = VIN;

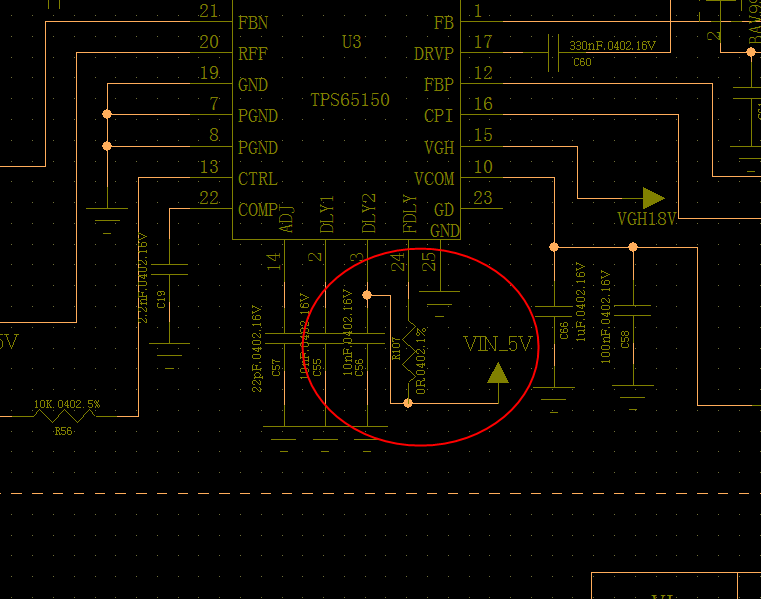

2. After changing the 100nF of the string between fdly and VIN to 0 ohm resistance, the 1.2M switch frequency is normal, the output is normal on VGL, and the 1.2MHz superposition level is normal on DRVN, but only 9.6V on VGL, and no output is available on DRVP,There is no action on the DRVP,Why is there no normal 1.2MHz stack level on DRVP,

3.I changed another application. I connected SW directly to the third pin of D20 without drvp voltage doubling. At this time, there can be 23v voltage on CPI, but VGH still has no output. I checked that the level of other pins in IC is vdly2 = 0V, vadj = 0V. What is the specific reason for this?