Other Parts Discussed in Thread: TIDA-010015, , UCC28064

Hello!

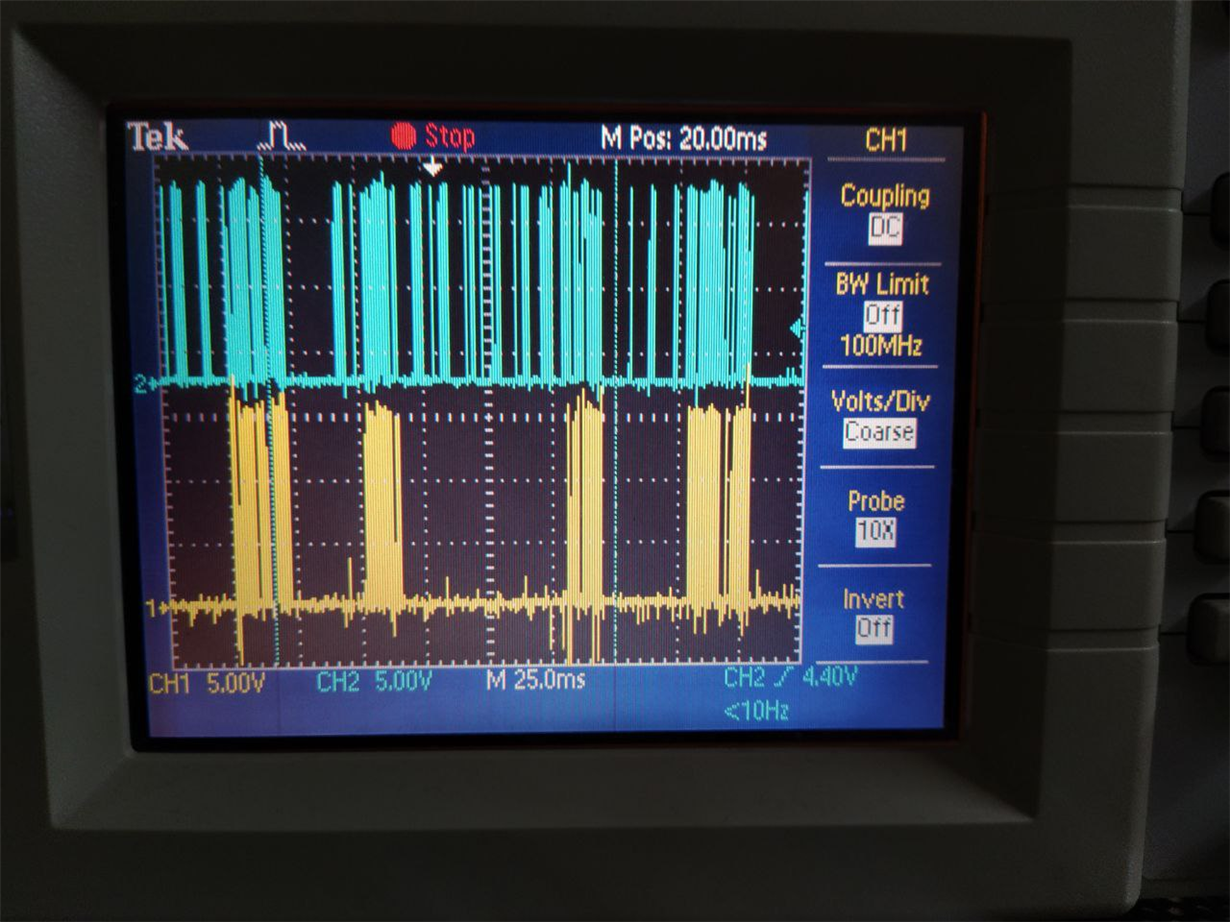

I am developing a 220-48V PSU based on TIDA-010015. I now have a problem of inconsistency between theory and practice regarding PHB and BRST pins. I saw on this forum somewhere, that this:

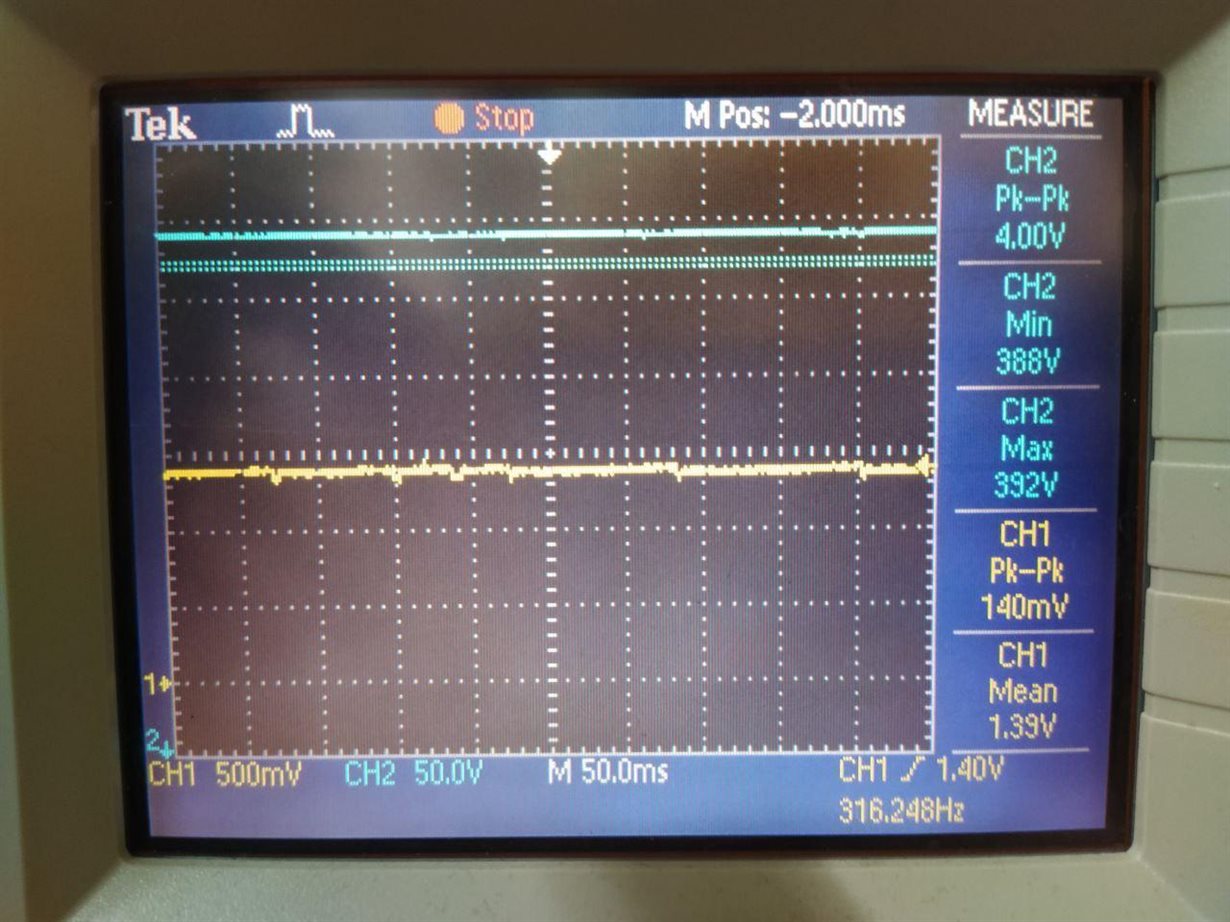

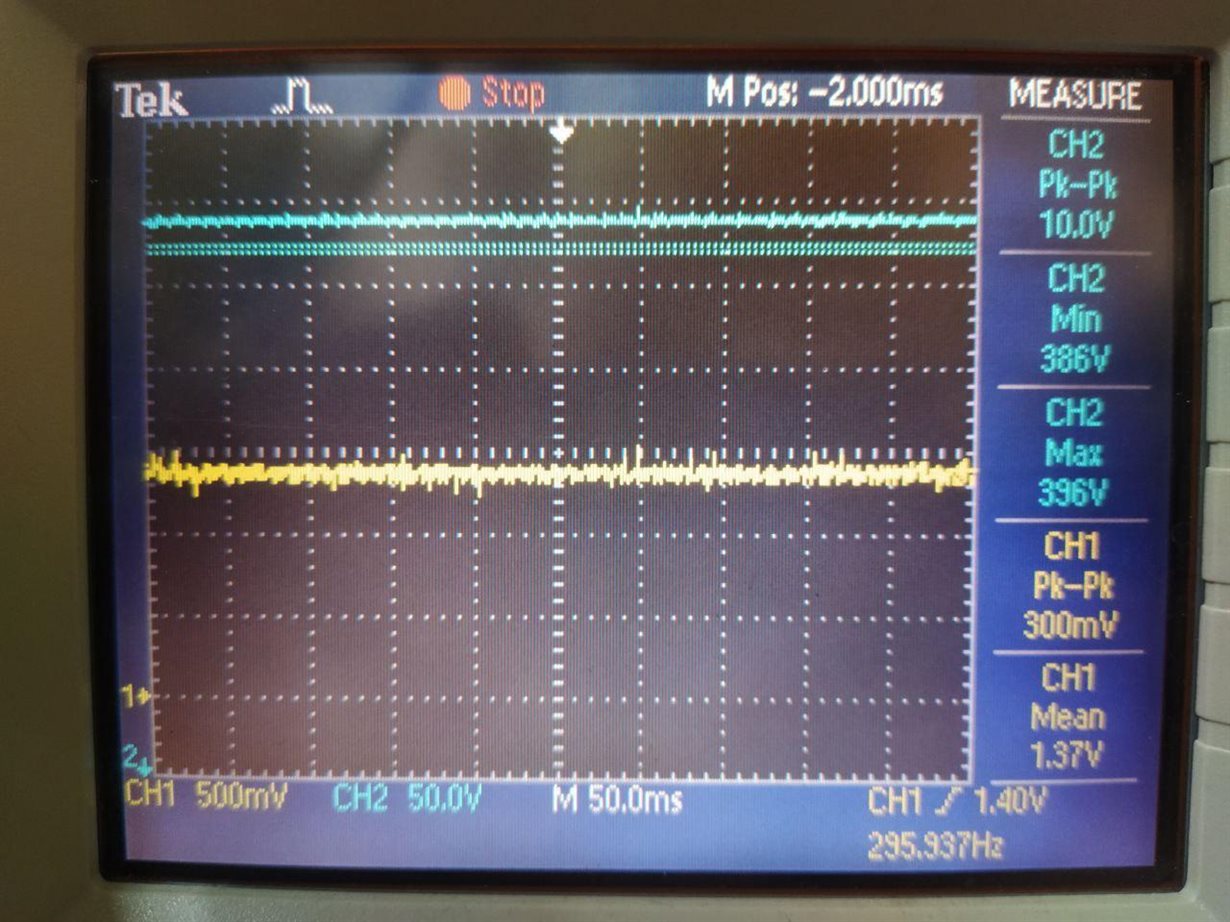

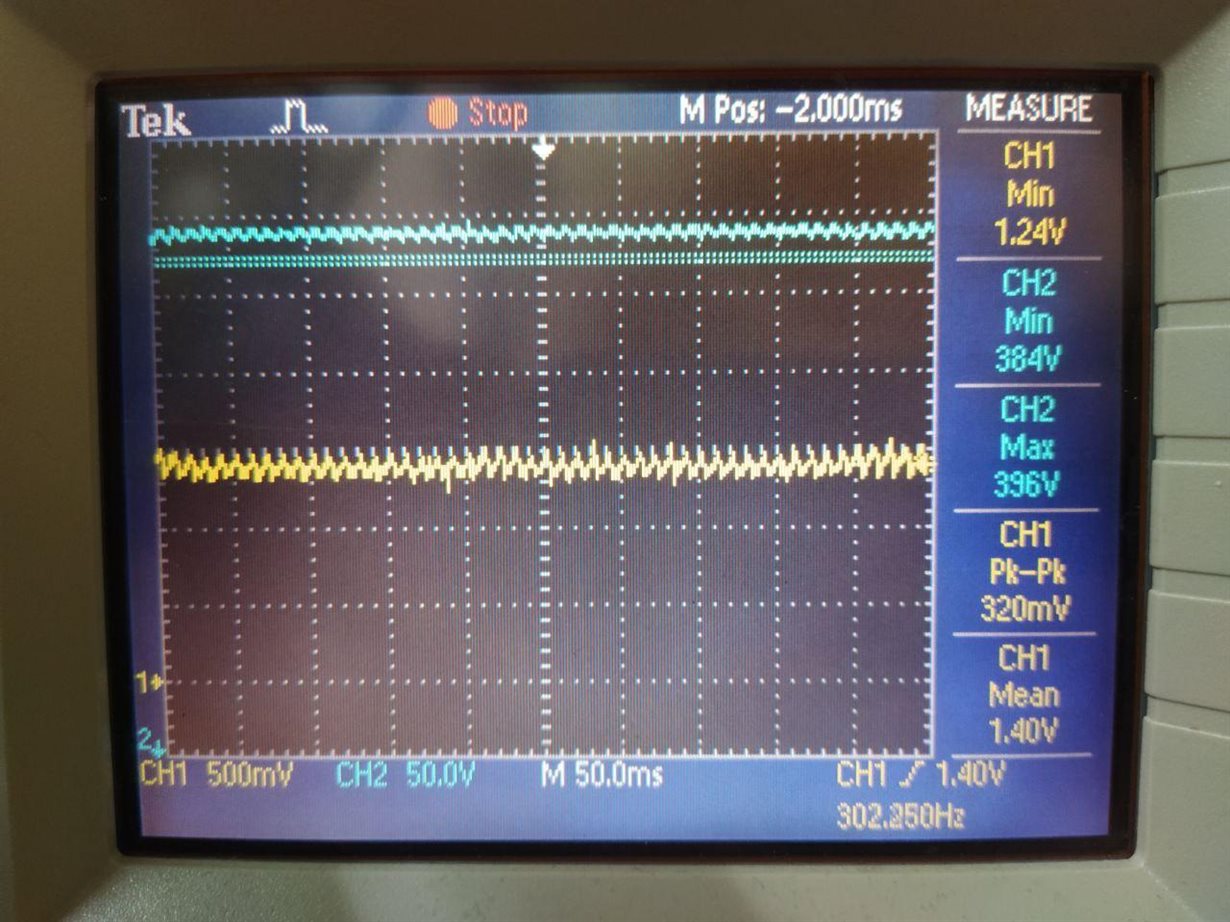

from page 22 of datasheet for UCC28064A is incorrect - there shouldn't be Vref. So with this taken into account, Burst mode and PHB thresholds are calculated so that they would be at approximately 60% of maximum power. I saw that at 50% load this design would come out of Burst mode and single-phase mode, which corresponds to calculations. So I changed R41 to 37.4 kOhms, R39 to 100 kOhms, R11 to 22.1 kOhms and R37 to 100 kOhms, so that BRST and PHD threshould would correspond to approximately 20% and 30% of maximum power (which by the way is set to 300 W by R7-R8, not 500W), and I still can't get the device out of Burst mode and single-phase mode at 50% of the load (meaning 150 W of load).

I also looked at the functional block diagram (page 14 of datasheet for UCC28064A), and there COMP voltage depends only on VSENSE, not in any way (at least the way I see it) related to current and so almost independent of output power (though a bit related to the VSENSE change rate, which correspond to loading resistanse).

So, I guess, i'm asking about how output power is related to COMP voltage and, therefore, to coming out of Burst and single-phase modes?

Regards, Aleksey.