Hi,

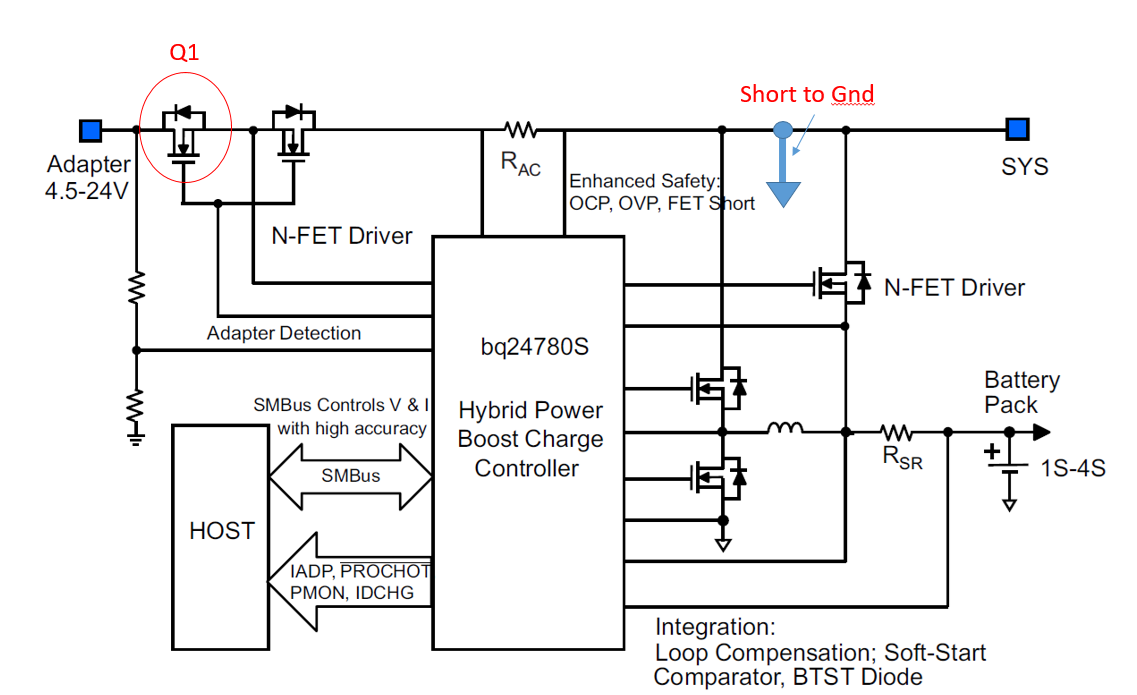

Now we need to test the robustness of the N-FET (Q1 as below), and tried to perform some stress (short-circuit) test it for it. The test steps are,

- Step1. Short SYS to GND.

- Step2. Plug-in adapter

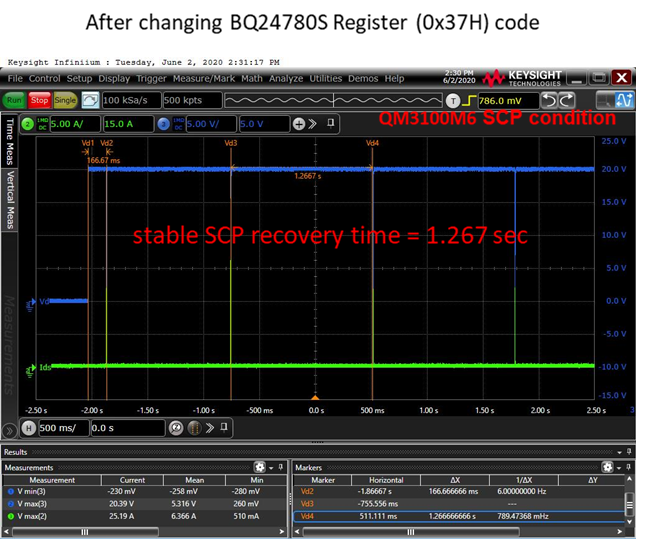

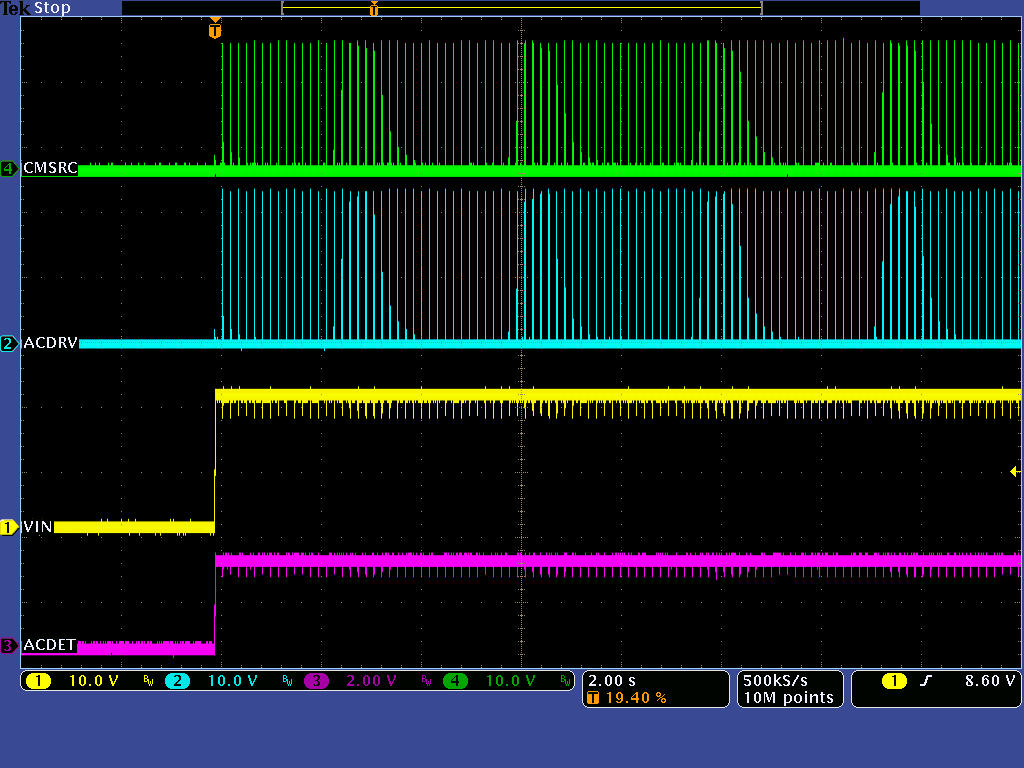

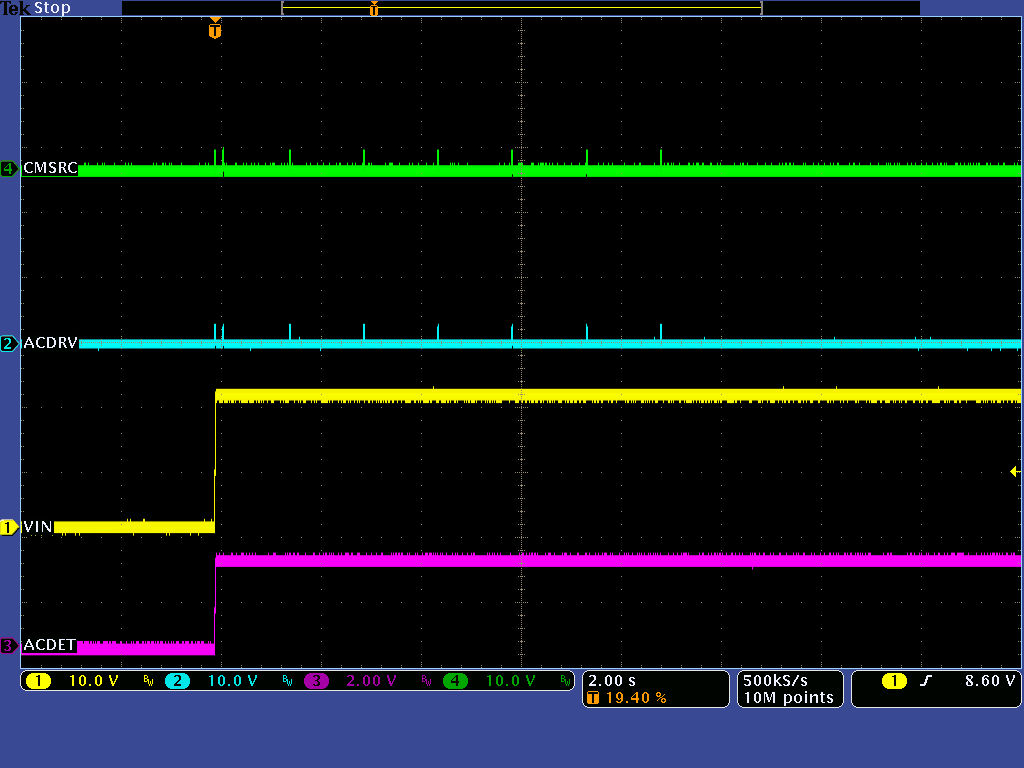

At this moment, we observe a 11~13A current spike lasting for ~1ms triggered periodically each 1.3 sec as below.

Since the 1.3sec internal is too long, the FET temperature is not rising high enough. Is there any way we can shorten the interval of 1.3 second to around 150ms? Or you have better suggestion to damage the FET on purpose?

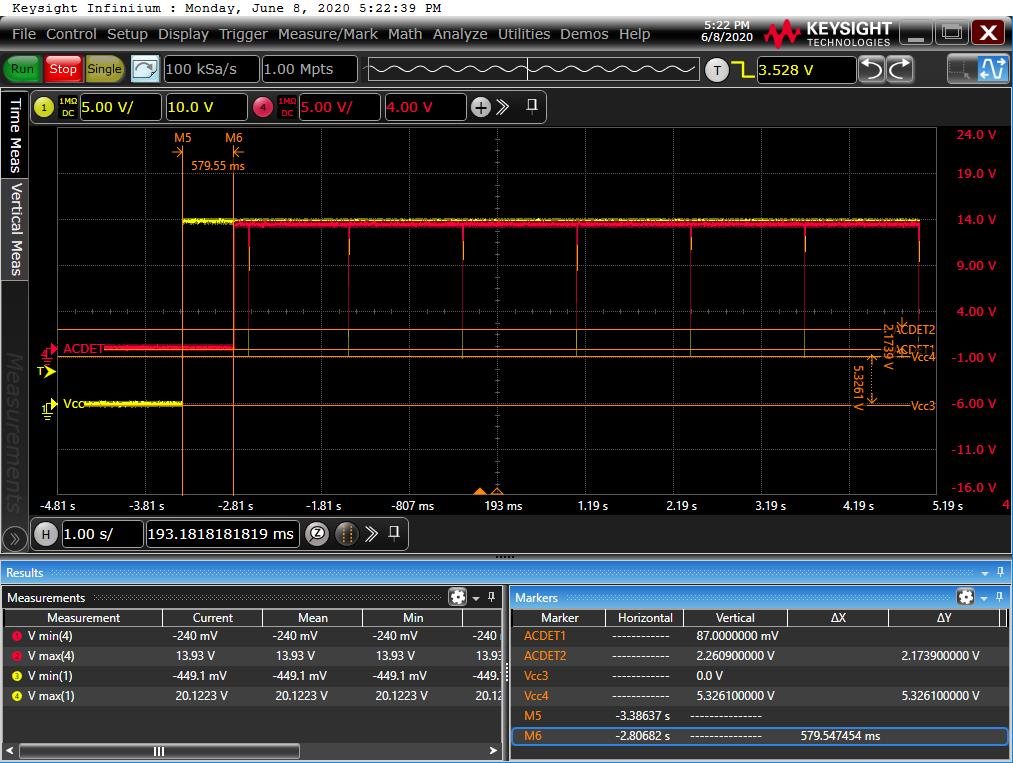

We've tried to set 0x37[12] ( ACOK Deglitch Time for Primary Input (ACOK_DEG) ) to '0' as shown below but seems no changes happen. Please help us to clarify it.

Antony