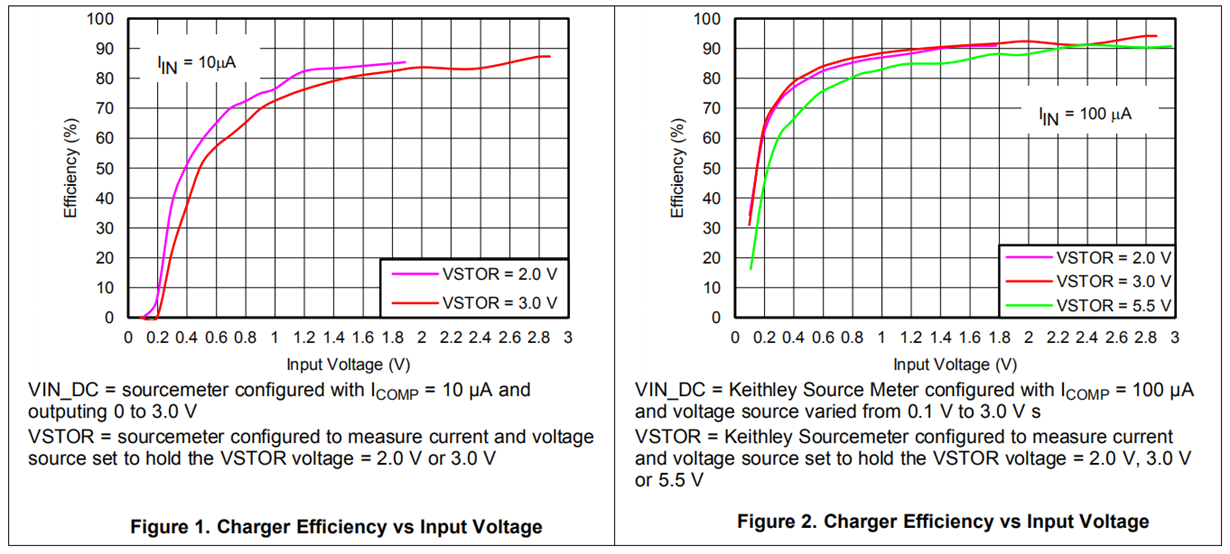

The BQ25505 model is encrypted and cannot be simulated by Tina. Then how can the charging efficiency diagram of the charging management chip data manual be obtained? Can it be simulated by software (such as Cadence)?Besides building the test platform, can we use other software to simulate the charging efficiency diagram in the data manual?The following figure:

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.