Other Parts Discussed in Thread: UCC256402

Hi,

I saw the following thread.

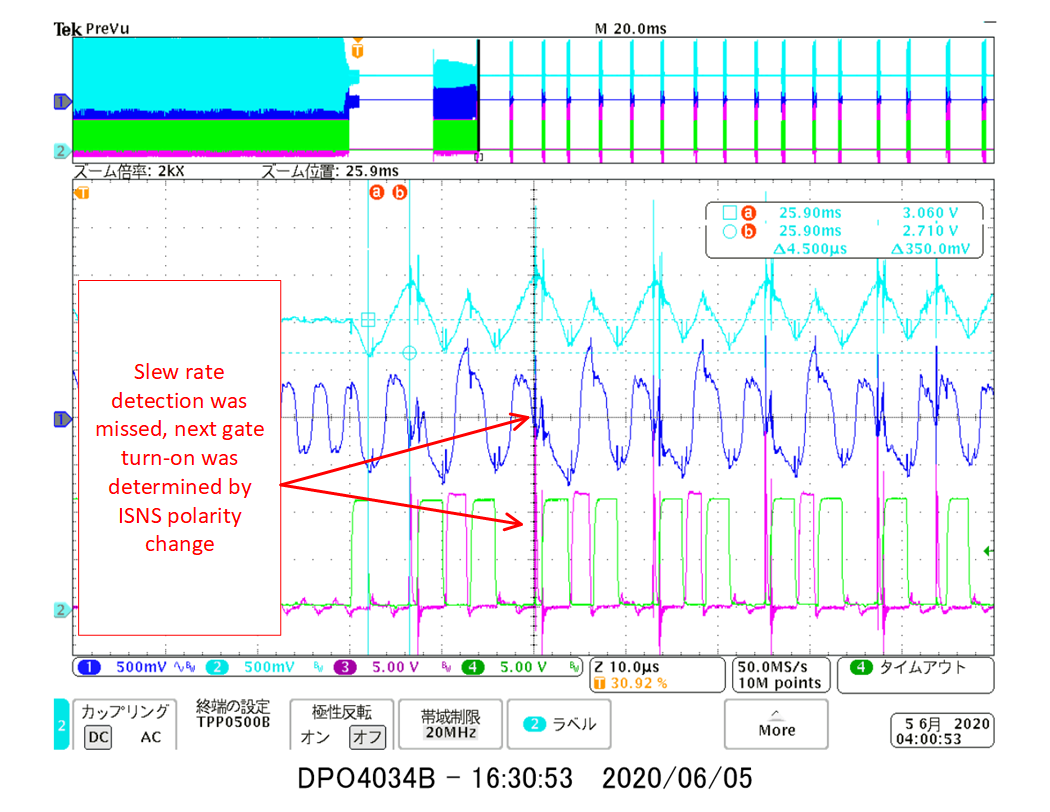

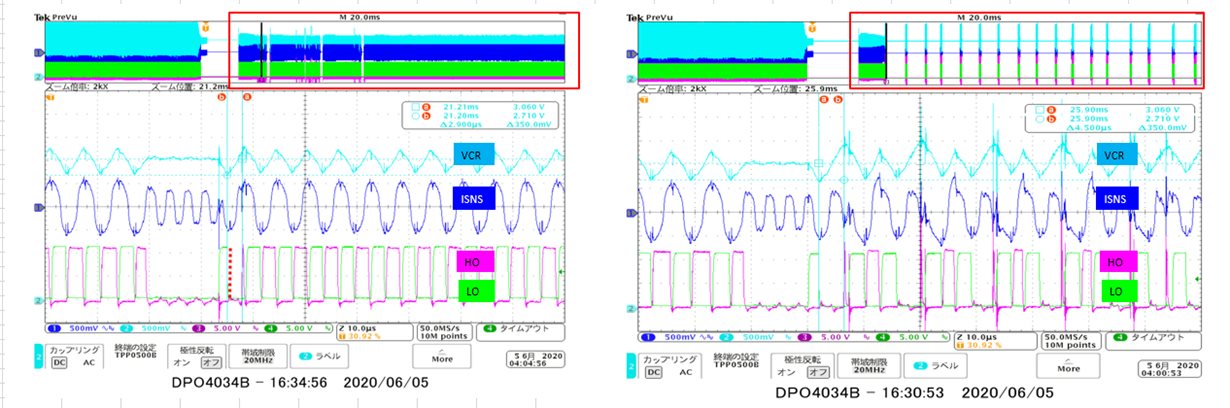

Mike-san commented that "I believe what your are observing is the converter detecting zero current switching ".

To confirm whether my understanding correct, I would like to know that the assumed ZVS detection timing.

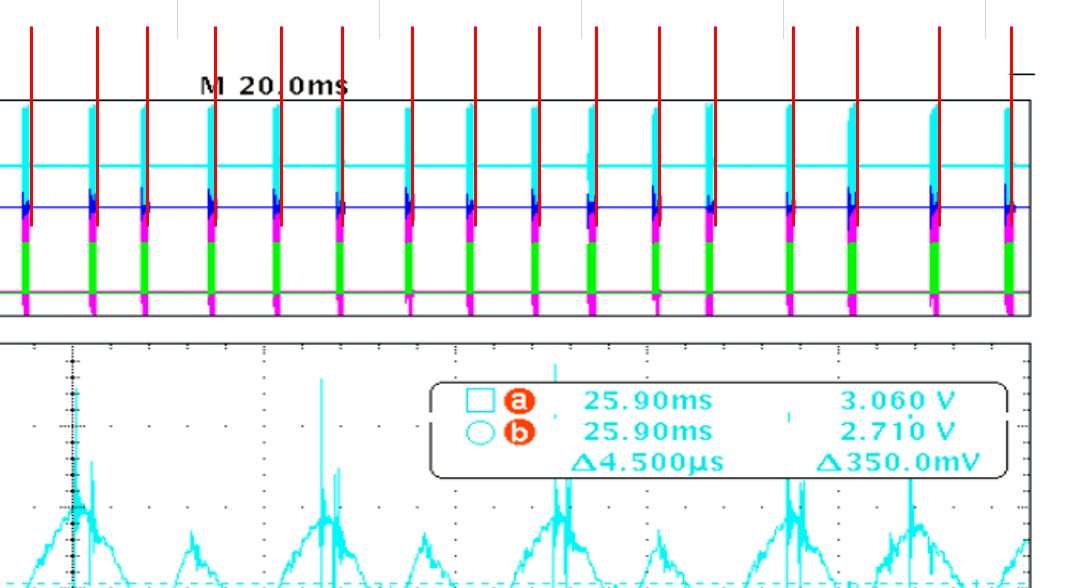

Is it assumed each red line timings on the following picture and the attached file?

Best Regards,

Kuramochi