Hi Gerold,

This is a related Question : https://e2e.ti.com/support/power-management/f/196/t/848080

I have completed the design using TPS548B22 for Generation of 0.72V

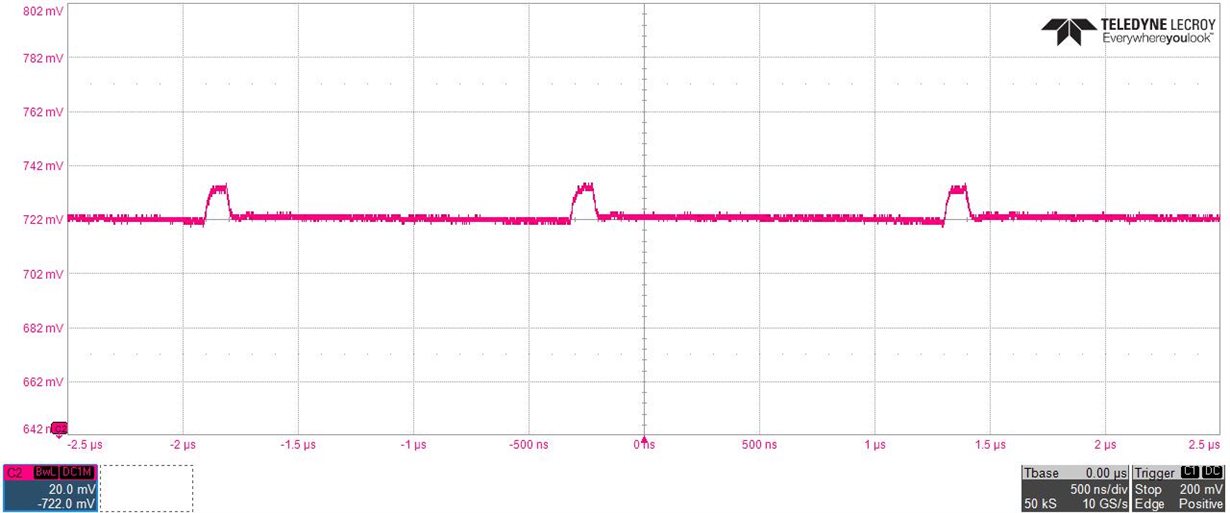

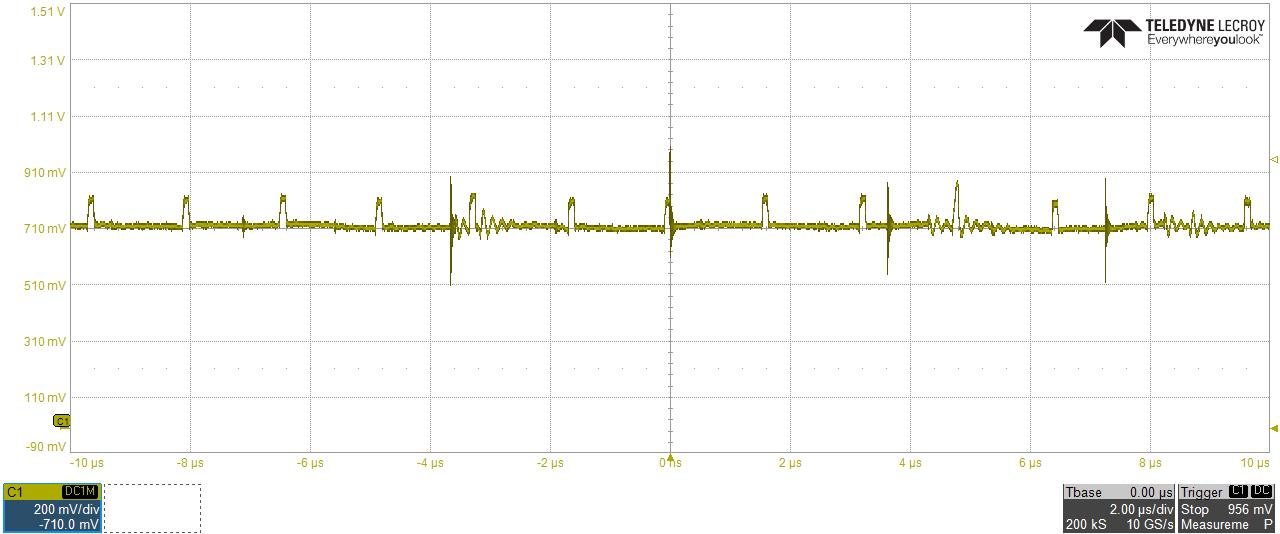

But below is the observed output after fabrication and assembly

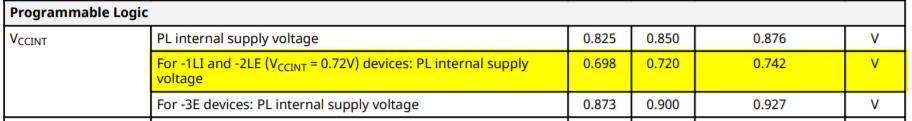

The recommendation from the FPGA OEM is as below

Why is the over shoot in voltage ?

Schematic Implemented :

I have used a external independent regulator to enable it, not any PMIC.

Scope shots at output node and switching node are as below