Other Parts Discussed in Thread: CC2640R2F, OPA2991, TPS62840, , TPS65131

Hello. I wish to ask some questions preparing my TPS65130RGER prototype;

this is a project using a 3.7V Lipo battery powered CC2640R2F Bluetooth project.

This 3.7V battery will be connected to TPS62840 and TPS65130RGER where the boost converter TPS65130RGER will power OPA2991 Op Amp by creating ± 15V.

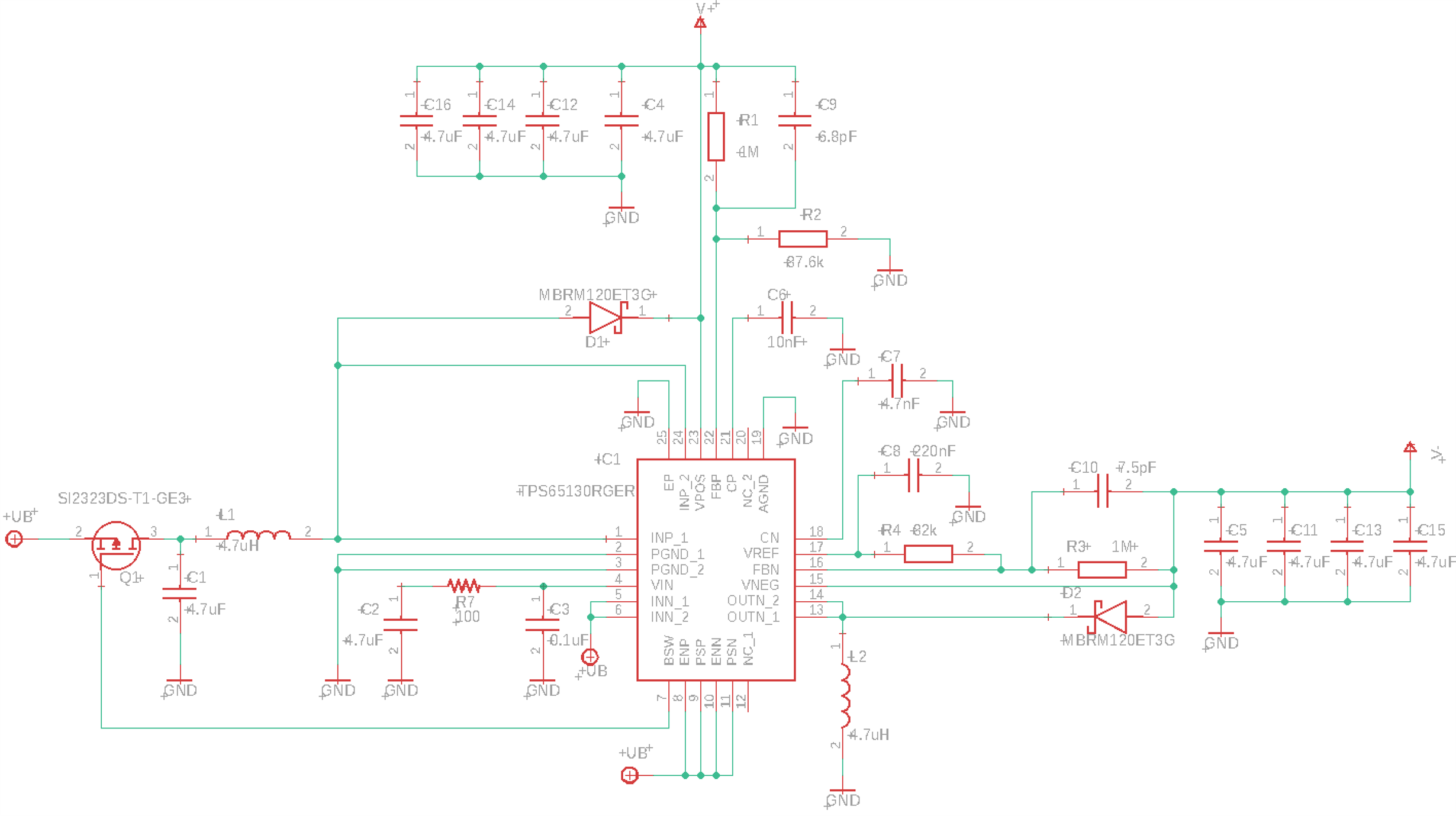

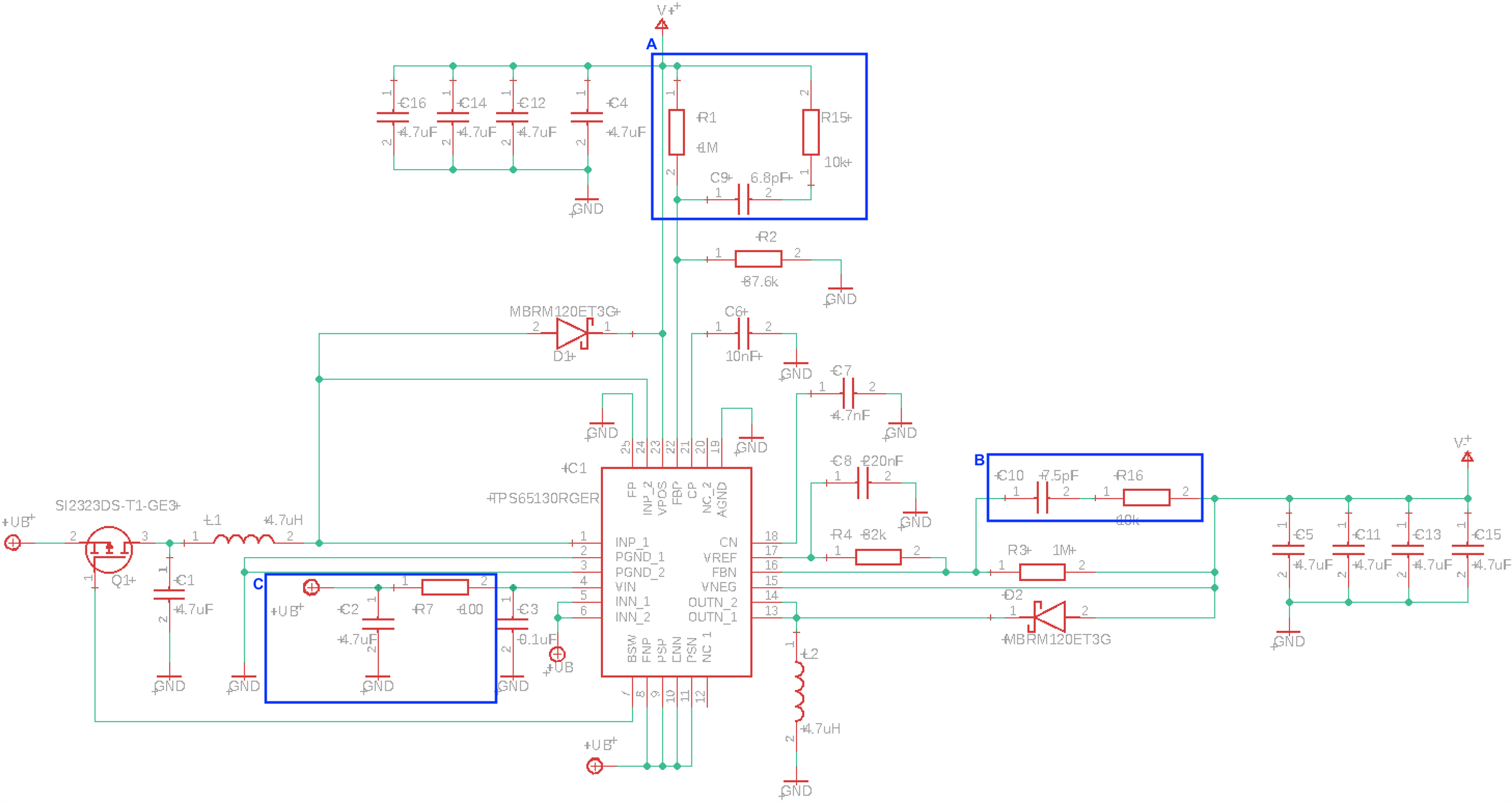

Here's my first draft of the schematic of the TPS65130 with the BOM;

My questions are

Q0. the WEBENCH Power Designer doesn't support TPS65130, right? I hope the WEBENCH support this device in the future.

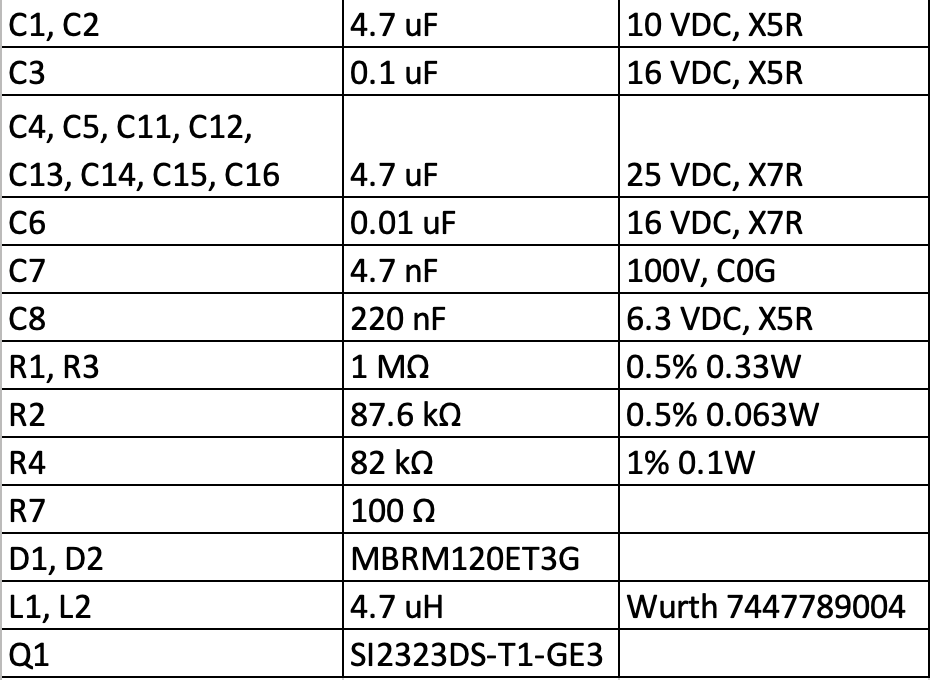

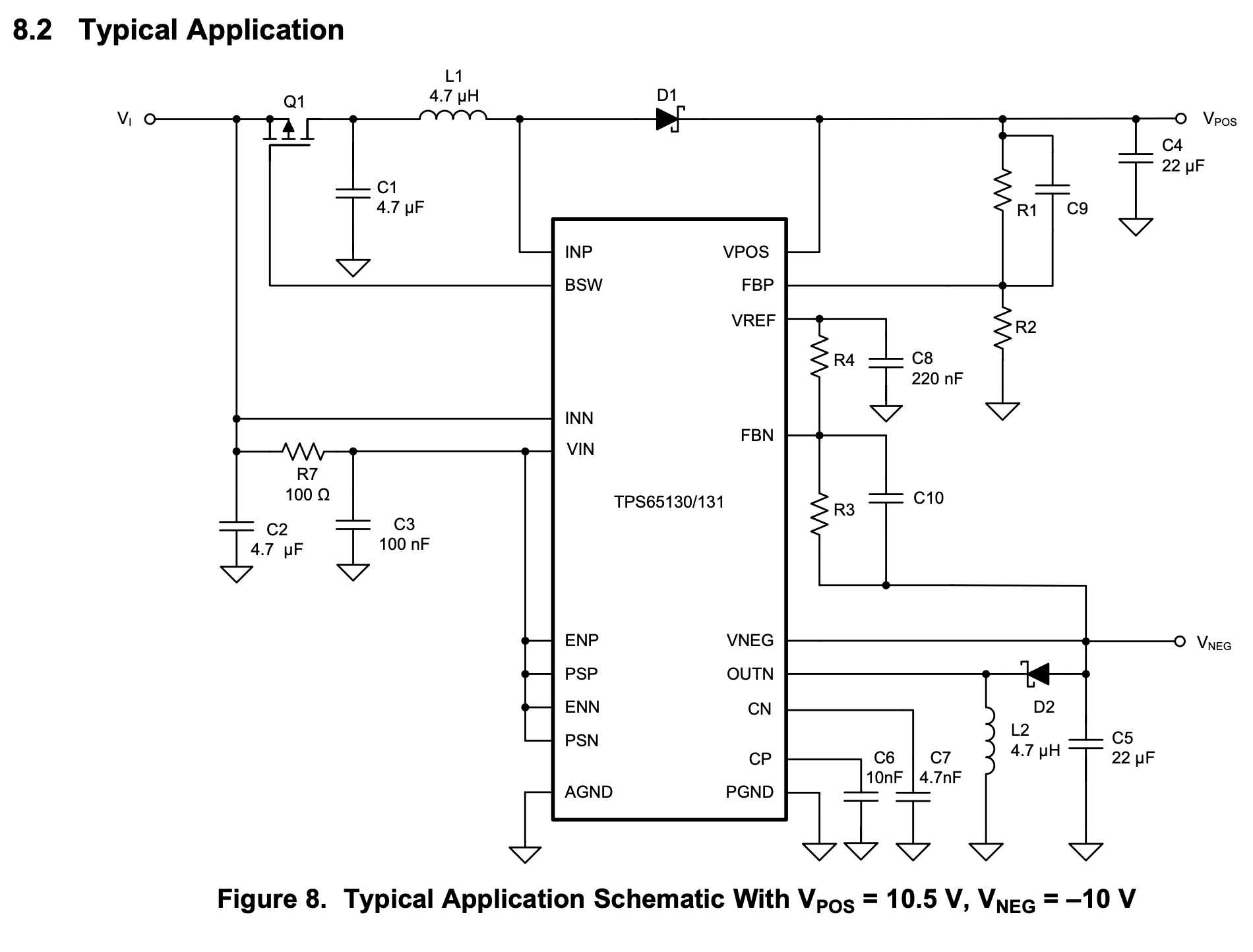

Q1. when comparing the design from the TPA65130EVM-063

VS

From the TPA65130EVM-063, the R5 || (R6 + C9) connection is different from the datasheet's R3 || C10.

Right now, I used the datasheet's calculation method

C9 = 6.8us / R1 = 6.8pF

C10 = 7.5us / R3 = 7.5pF

Currently, I copied the datasheet's design; which one should I follow and how was C9 from TPA65130EVM-063 was calculated?

Q2. About the four control pins (ENP PSP ENN PSN), can I connect all four pins to a single 3.3V/0V GPIO pin from the CC2640R2F MCU?

I only want to toggle a single GPIO to set the voltage to HIGH/LOW for these control pins.

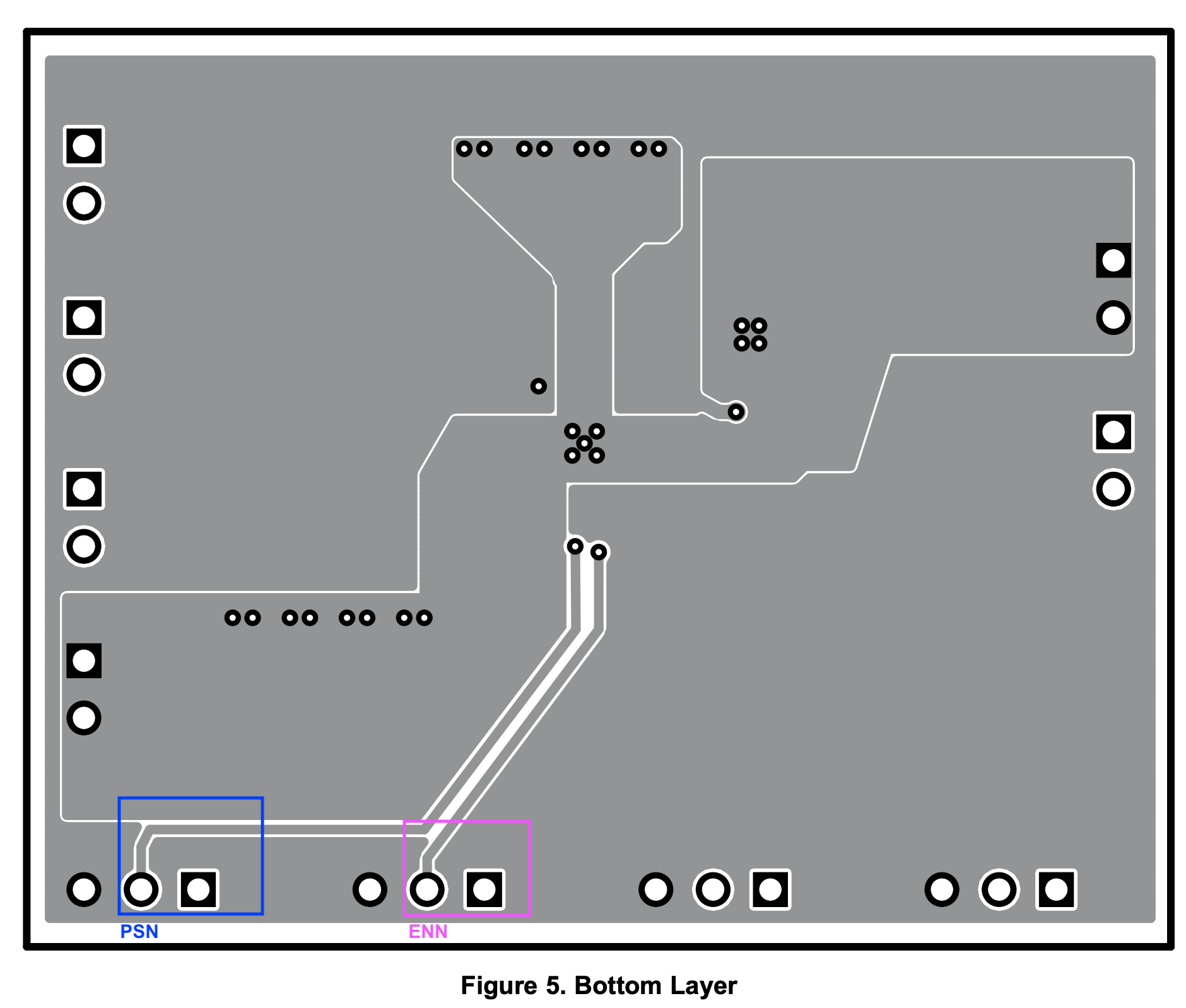

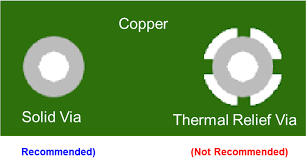

Q3. Another discrepancy; TPA65130EVM-063 has 5 thermal relief vias

whereas the datasheet example showed 9 vias.

I'm creating a 2-Layer PCB (FR-4, 1.6mm thickness) for my prototype.

What via size (Diameter / Hole in mm) and number of thermal reliefs are recommended to power the OPA2991 Op Amp when using a 3.7V LiPo battery?

I use EAGLE 9 and I was using this link to generate these vias.

Q4. Setting the voltages when V_ref = 1.213V,

R1 = R3 = 1 MΩ, R2 = 87.6 kΩ, R4 = 82 kΩ

R1 = R2 * (V_POS / V_ref - 1), V_POS = V_ref * (1 + R1 / R2) = 15.060 V

R3 = -R4 * V_NEG / V_ref, V_NEG = -V_ref * R3 / R4 = 14.793 V

The datasheet says

"The maximum recommended output voltage at the boost converter is 15 V. To achieve appropriate accuracy,

the current through the feedback divider should be about 100 times greater than the current into the FBP pin.

The recommended value for R2 should be lower than 200 kΩ.

The recommended value for R4 should be lower than 200 kΩ."

I want to achieve ± 15V. Do I need to change the resistors due to reasons like my current V_POS > 15?

Since '6.1 Absolute Maximum Ratings' says 'VPOS max 17V', I wish to check this part.

If there are additional changes needed in my schematic, please let me know. Thanks for your help.