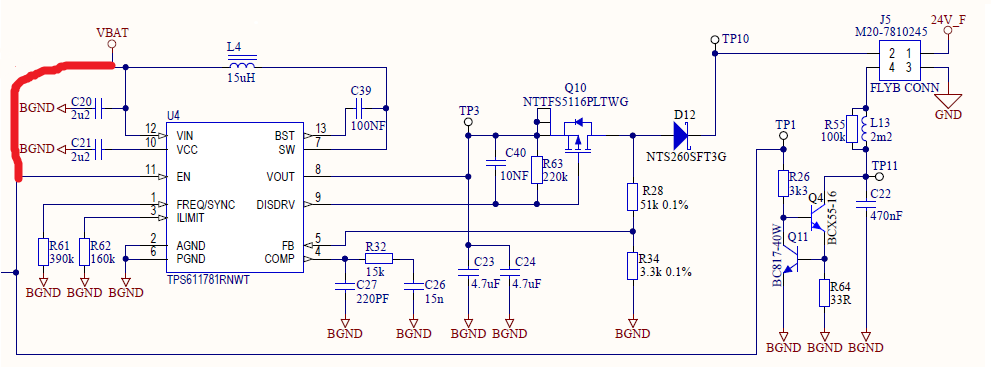

I'm writing to ask if you could help us with some technical difficulties that we have using TPS611781 boost converter. We use it to boost battery voltage from 2.7Vmin (triple NiMH AAA) to 19.5V.

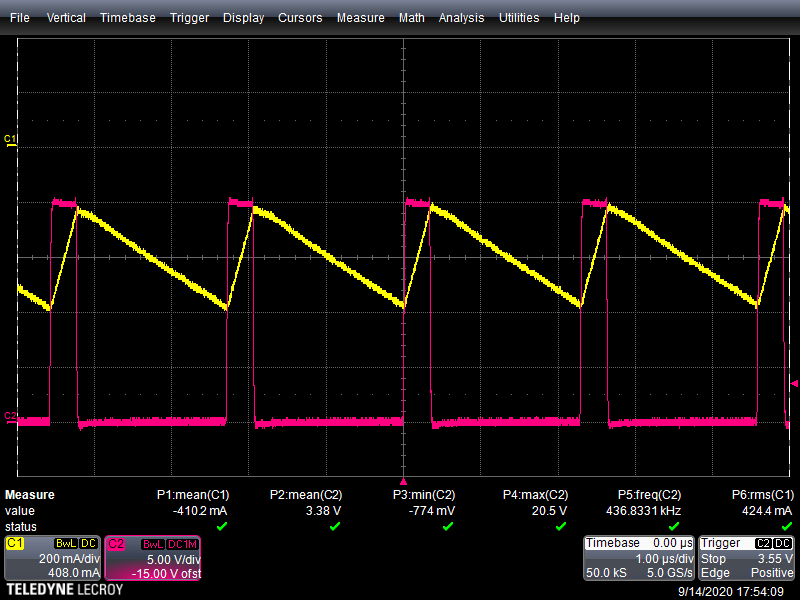

The first issue is that efficiency is much lower than we expected, based on design calculated by TI webench. As in the attached webench report, we expected 87.5% with Vin=2.7V, Vout=19V, Iout=50mA but according to out measurements we get only 74.5% with Vin=3.0V, Vout=19.7V, Iout=50mA. Better inductor didn't help much but lower frequency improves the result (84.5% is the best I got with frequency changed from 444kHz to 208kHz and lower resistance inductor PA4343.153NLT). It looks like switching losses are much higher than estimated by webench. Is this big error possible, or we do something wrong?

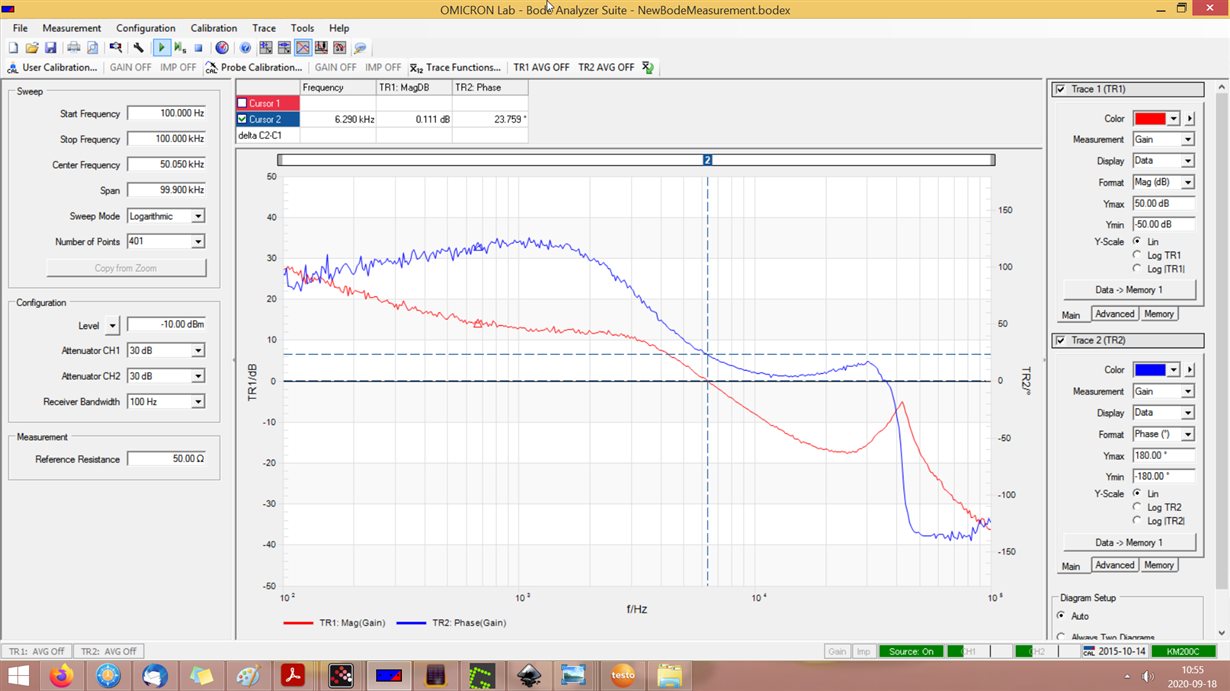

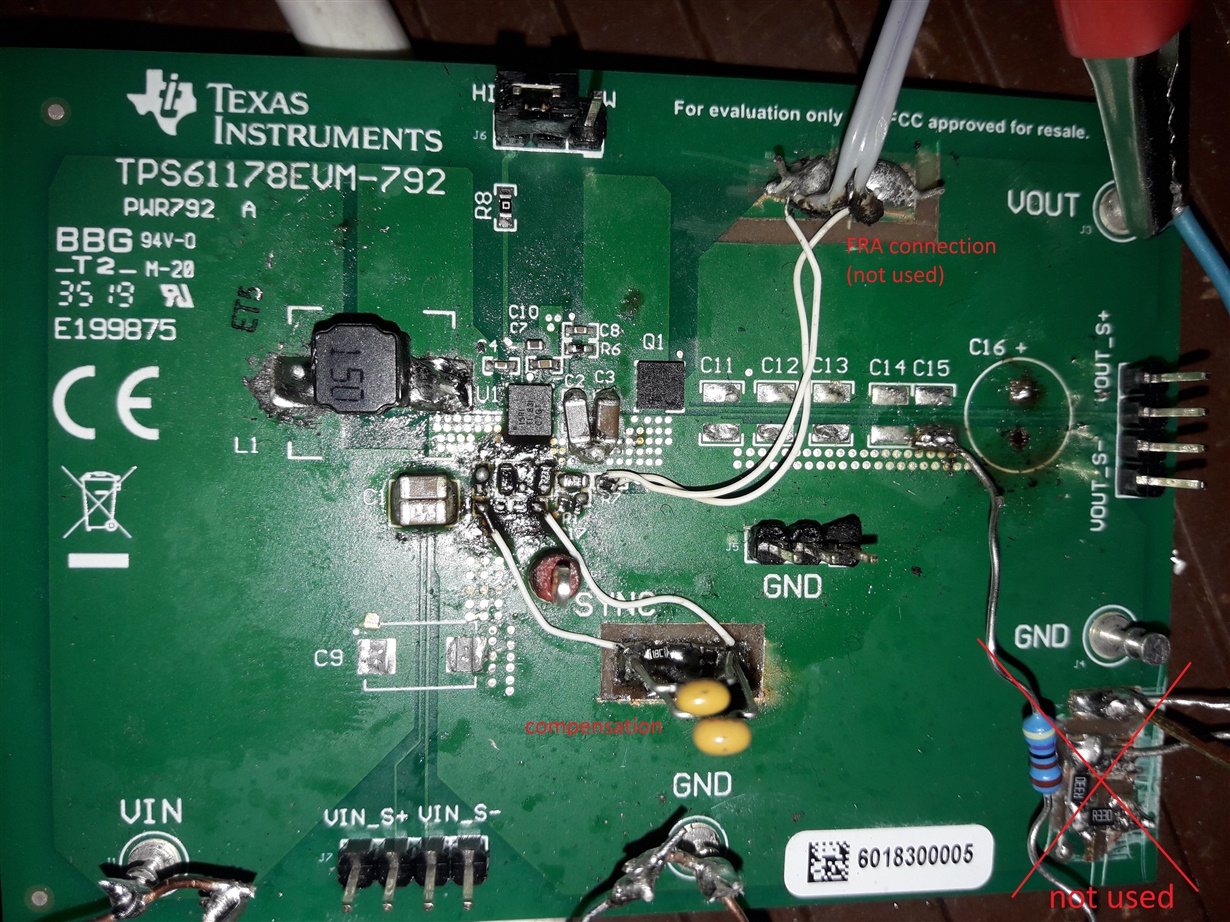

The second problem is that after decreasing the frequency some stability issues appears. The main problem is with this bump in frequency response, about 40-50kHz - see the picture below. It increases when voltage is decreased (worst case is our design minimum 2.7V), it depends also from other factors (better if output capacitance is higher, temperature lower, frequency higher, inductance lower). When it gets too close to 0dB the converter starts oscillating (input current is sinusoidal). I wasn't able to change this frequency by changes of the circuits components, only the attenuation, but we'd like to fix the problem without need to increase output capacitance (space limitations), increase frequency (efficiency issue) or reducing inductance (high efficiency at 50mA which 33% of full load requires this inductance). This frequency didn't change also if NiMH battery with short wires was used instead of power supply and this bump was observed also in measurements with different switching frequency.

Have you got some hints about where this frequency can come from and how to deal with this issue?

Schematic in the attachment (inductor SRN6045TA-150, enable shorted to vbat, changes for tests with fsw=208kHz: R61=820k, C27=2n2, R32=5k1).

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.