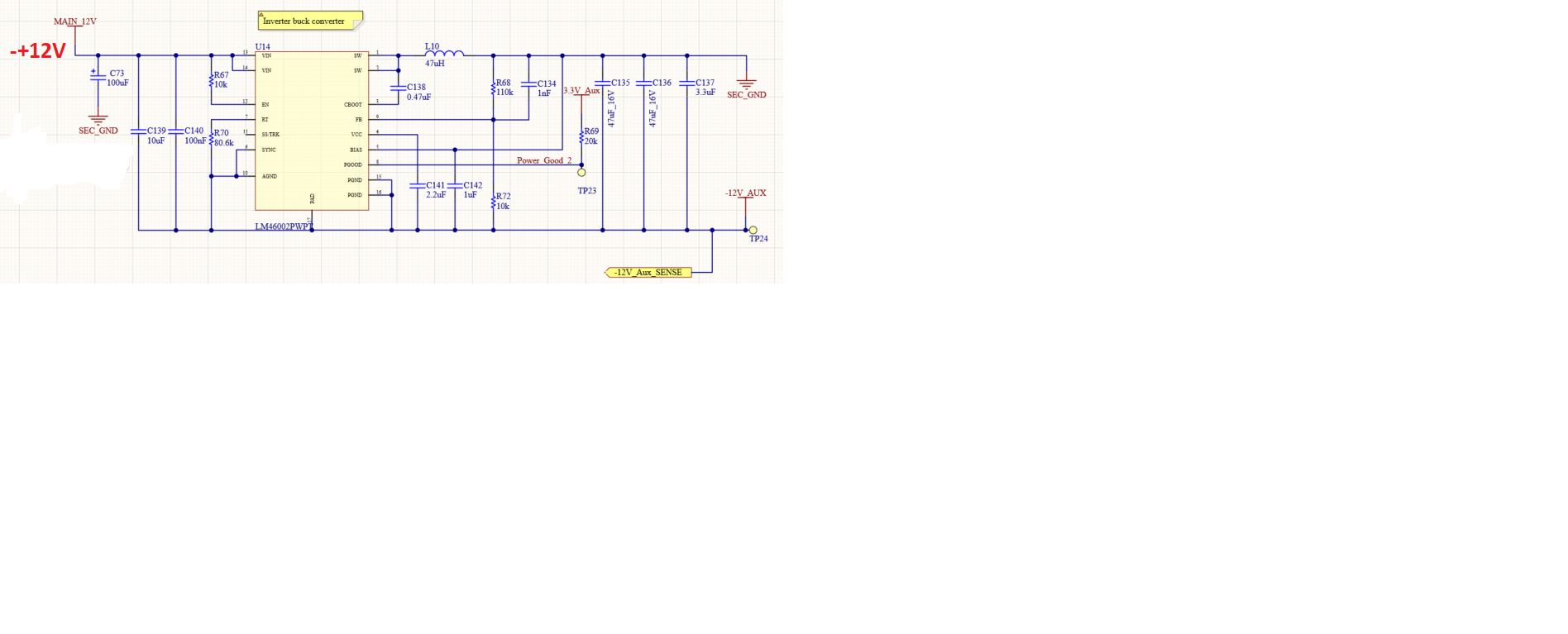

I am using LM46002 as an inverter in order to get -12V output when Vinput = +12V. The output voltage is correctly regulated at light load condition or low loads, but when I connect 1A load the converter output (-12V) is unstable and the converter is not able to regulate the output. I have realized that the LDO reference voltage (Vcc) drops below its UVLO (3.2V) and, in turn, the converter output is switched off. You can see the behavior of the output and LDO voltage in the following captures:

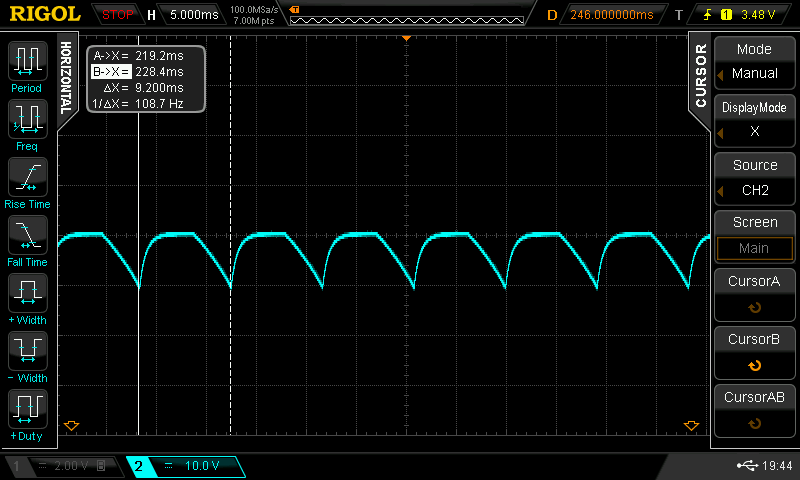

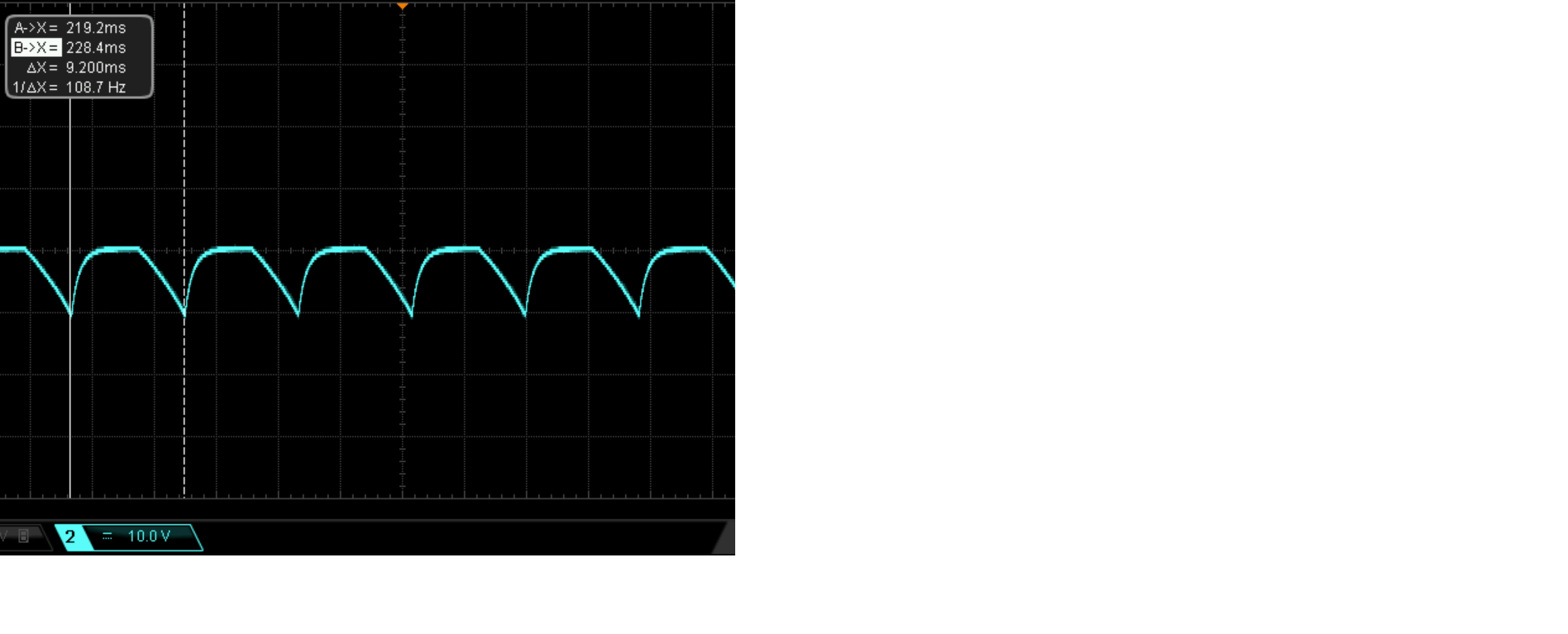

-12V output at 1A load:

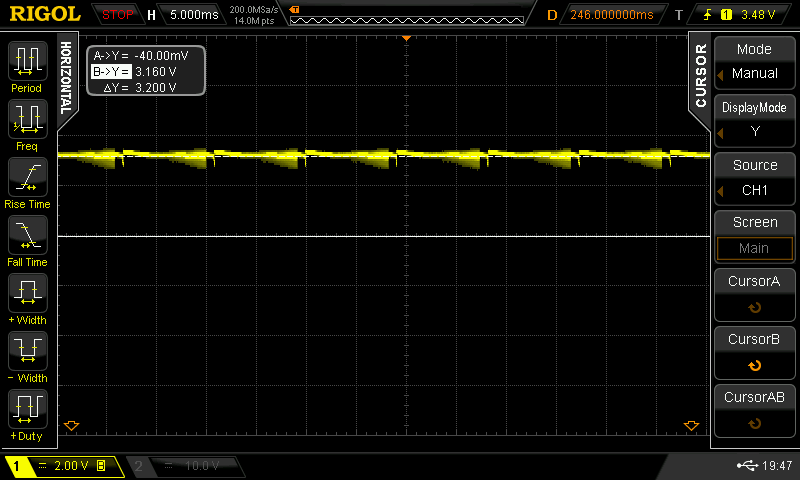

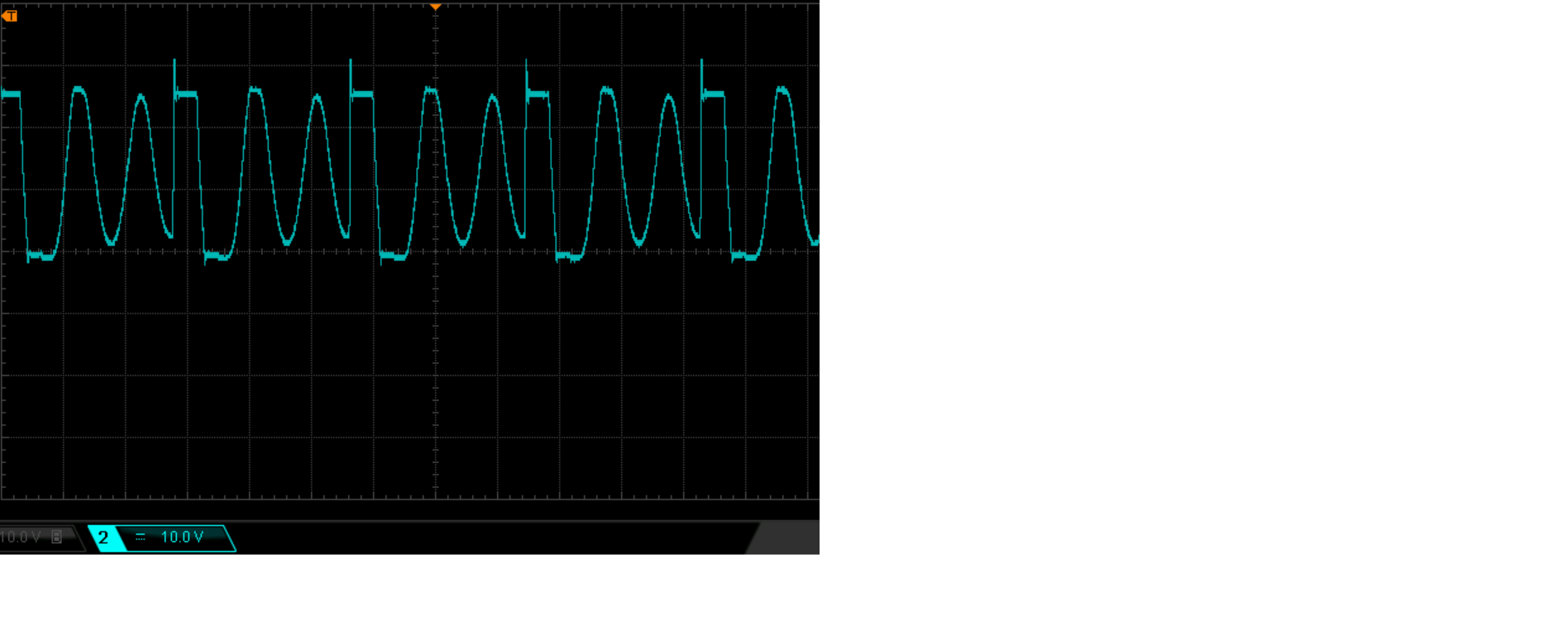

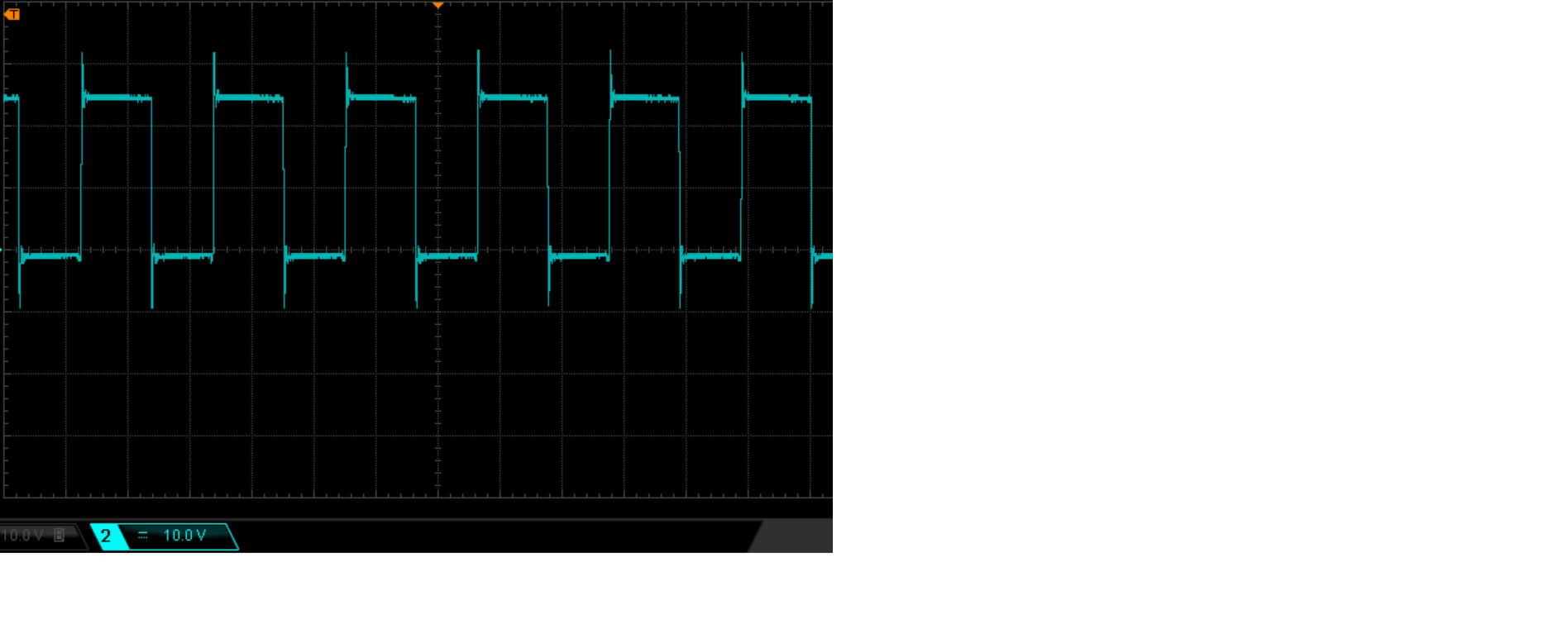

LDO voltage measured on Vcc pin:

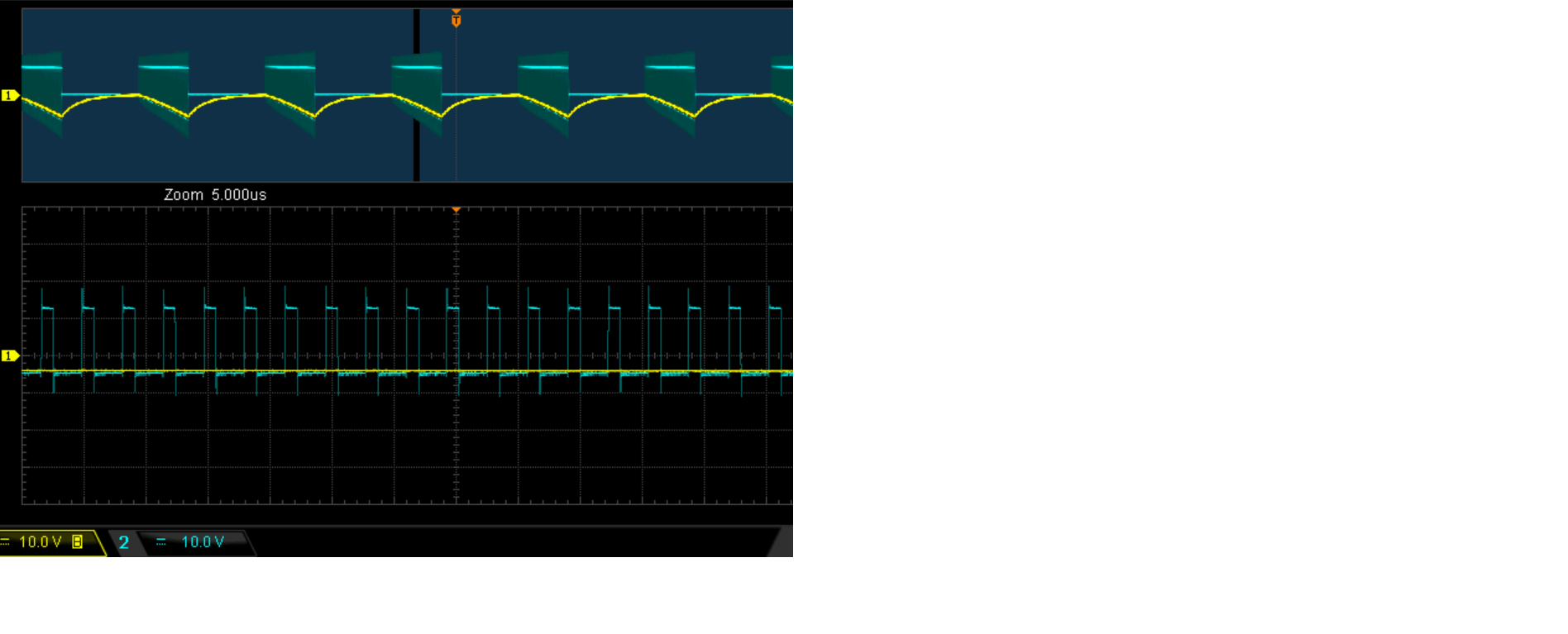

Why I get this behavior at 1A load? Please, see carefully the attachment (design schematic):

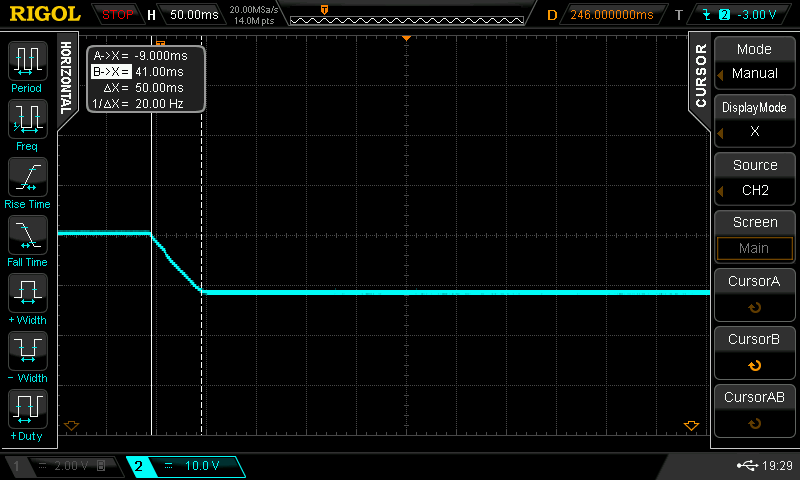

I am using the soft start by default of the converter. If I increase the soft start duration placing Css = 100nF, the output is correctly regulated to -12V at I_load = 1A.

I would like to understand the root cause of this issue. Thanks in advance for your support.