Other Parts Discussed in Thread: LM5155

Hoping you can give me a hint.

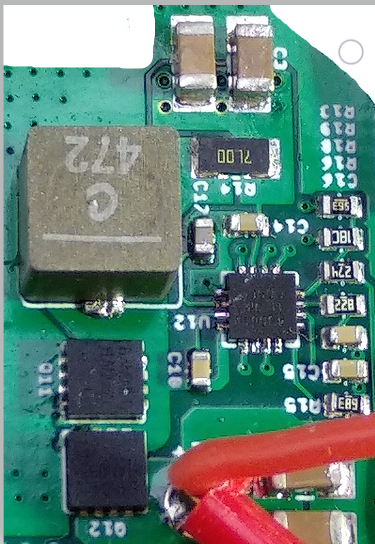

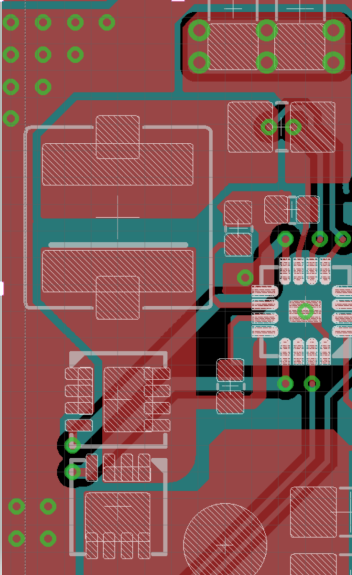

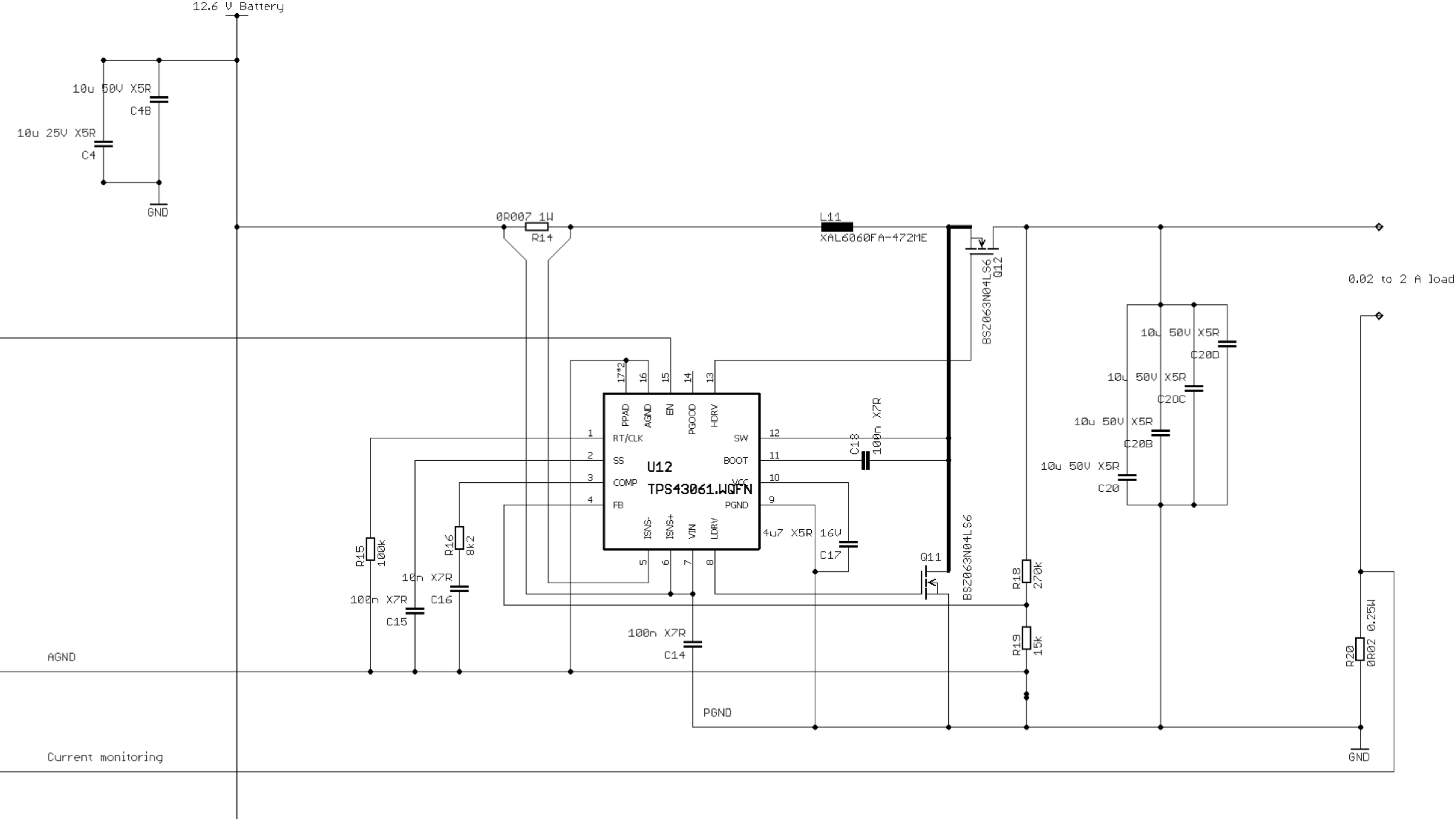

I used Webench and the TPS4306x design spreadsheet for guidance. I did what I think is a good layout (not my first switcher layout).

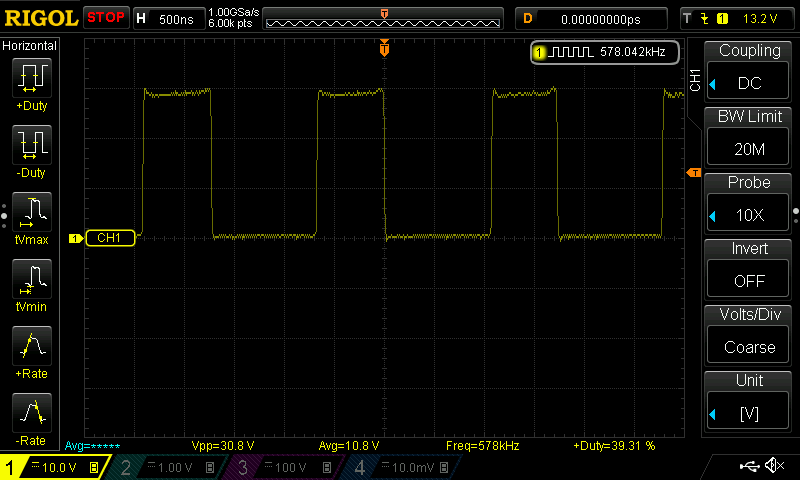

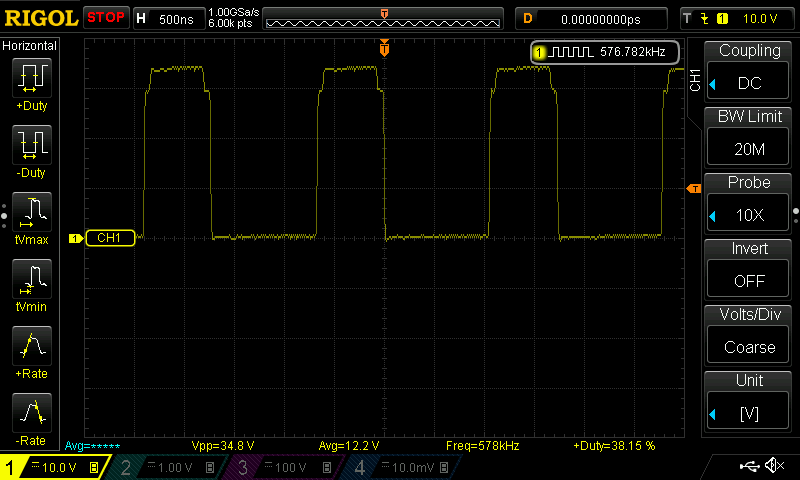

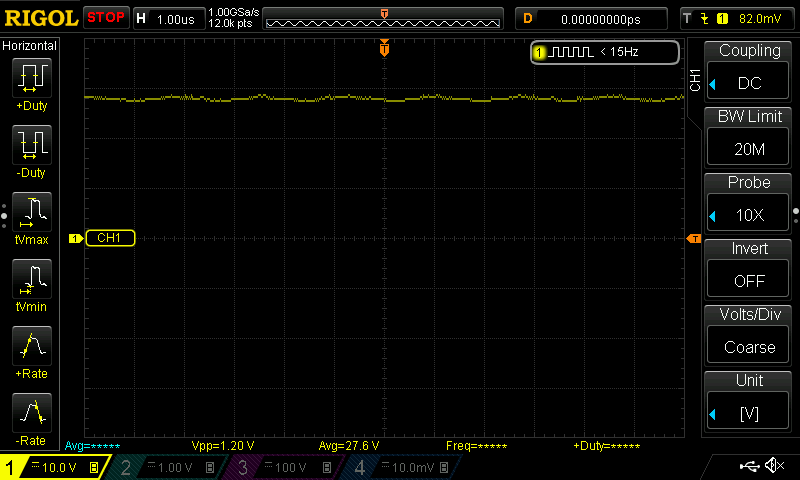

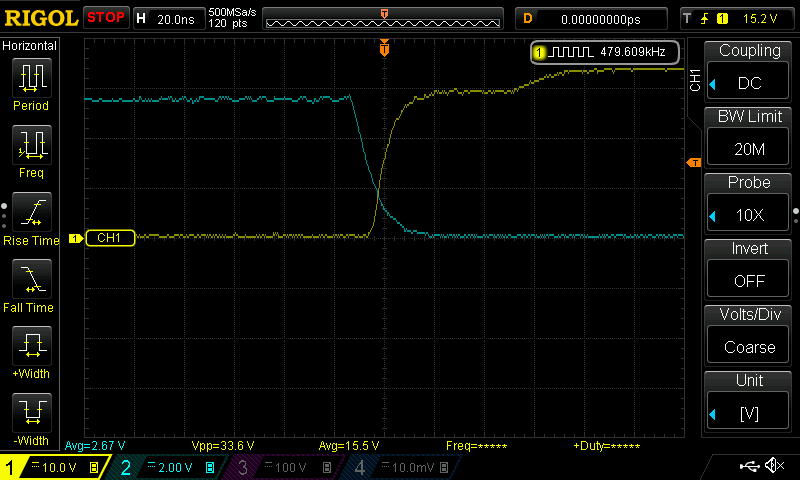

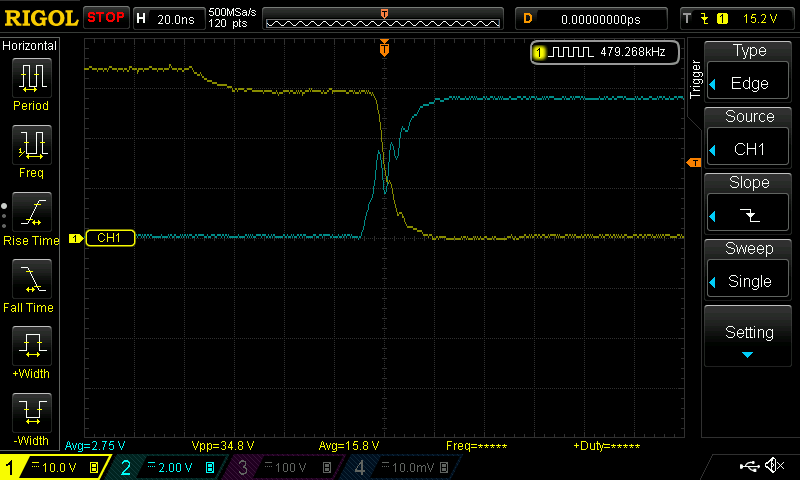

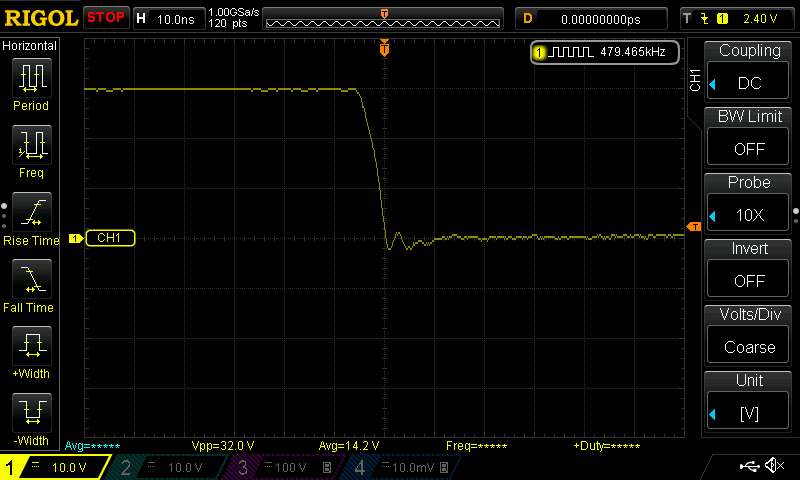

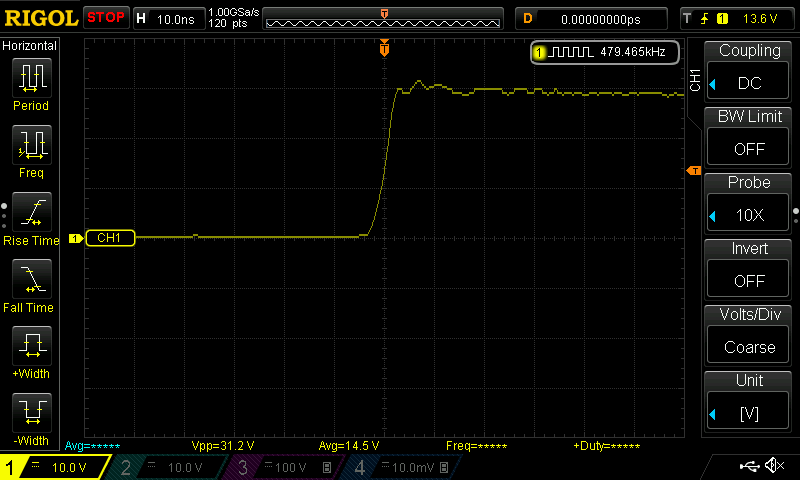

Switch node, current sense, hi drive and lo drive all scope good, up to ~66% output anyway. Vin, Vcc are stable.

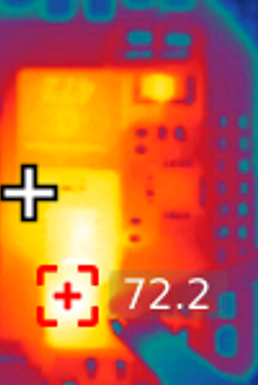

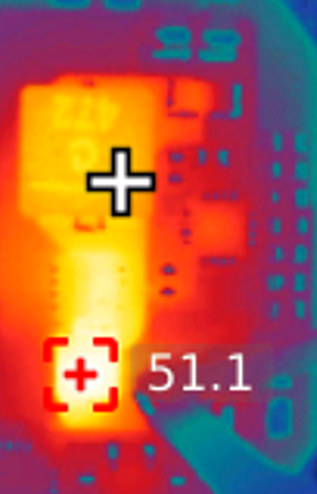

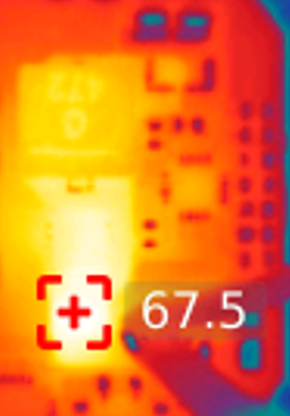

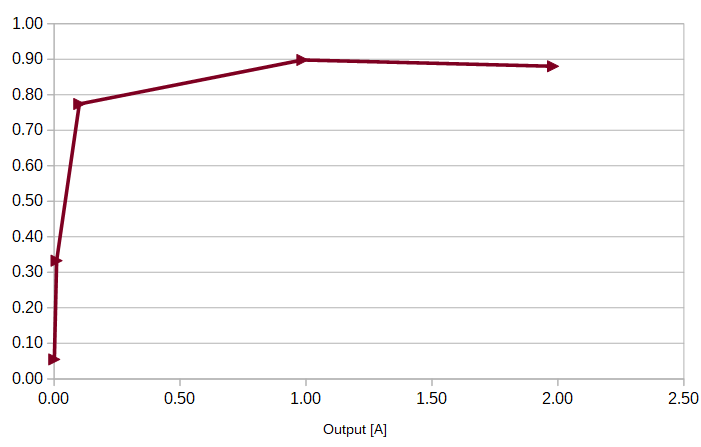

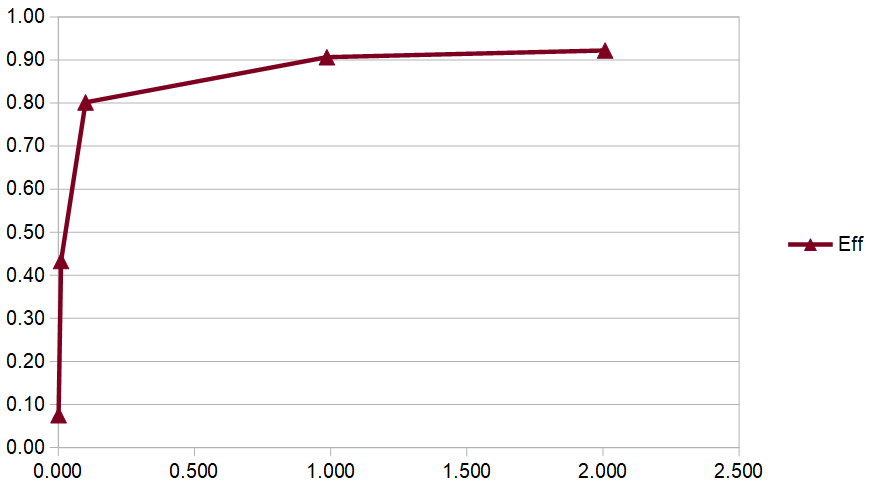

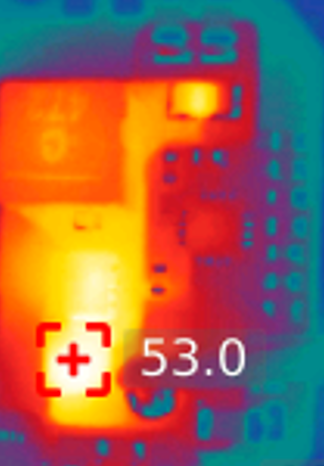

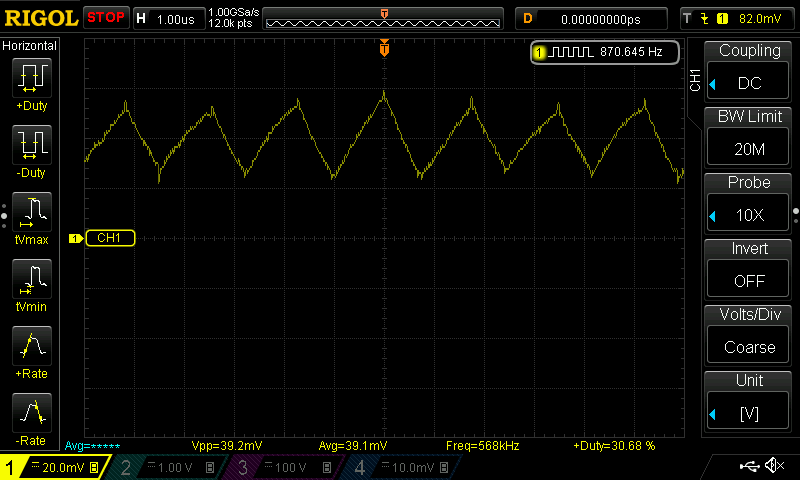

But I only get 88% efficiency and some sub-harmonics above 66% output.

The harmonics goes away if I add output capacitance. But the efficiency does not improve. The resulting heat is a show-stopper for the application.

Where should I look?

Details:

10-12 V in, 27.5 V 0-2 A out. Output ripple spec is not very important.

4-layer board with tight layout, tight loops for high and low drives.

Fs = 820 kHz (68 kohm)

Inductor is an XAL6060 4.7 uH (14.4 mohm)

7 mohm current sense

FETs are Infineon BSZ063N04LS6 (6.3 mohm, ~6 nC)

Cin = 2x 1206 Samsung 10 uF 50 V X5R

Cout = same

No RC filtering for the current sense (board space is tight).

Aiming for 94-95% efficiency.

Thanks!