Dear TI Team,

I have a question about the WATCHDOG TIMER IC.

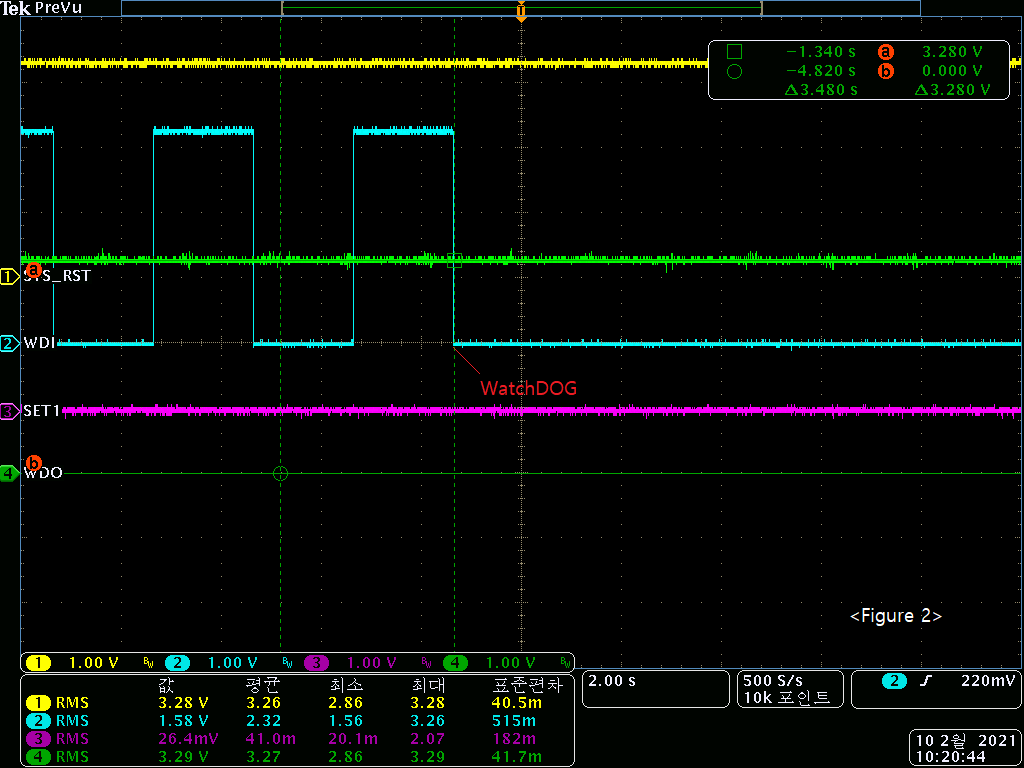

As far as I know, if SET1 is set to LOW, WATCHDOG is disabled and /WDO is asserted as LOW.

Is there a case where /WDO is output high even if SET1 is LOW?

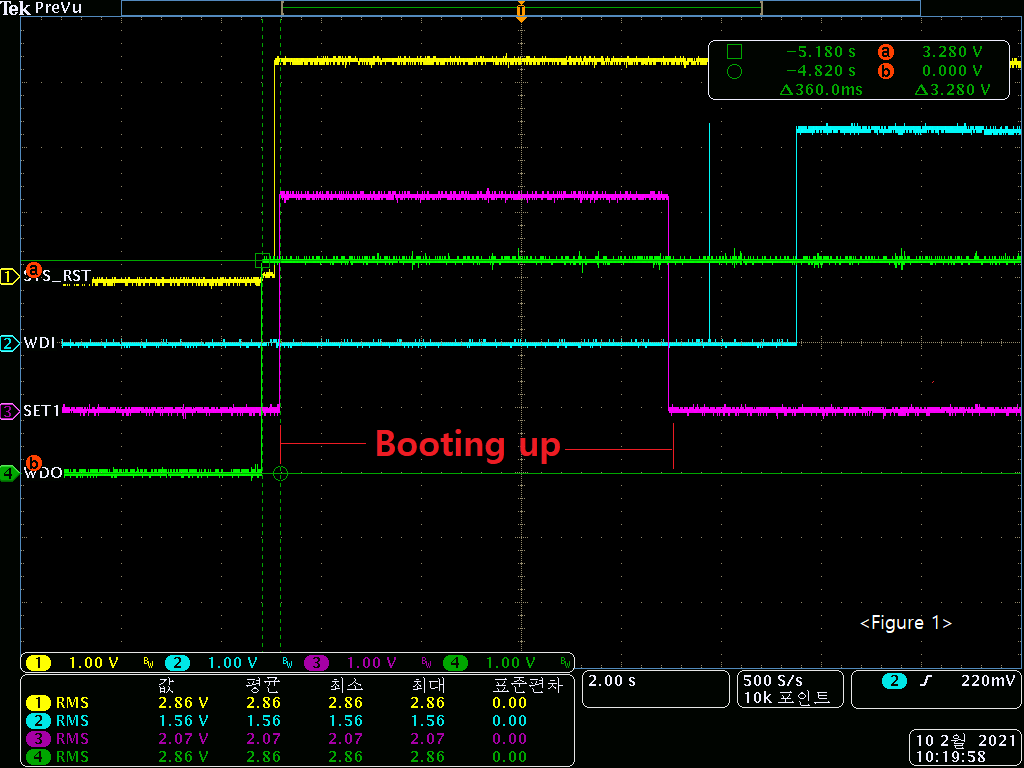

I couldn't attach the waveform, but /MR is High, /REST is also High, and SET1 is kept high for about 1-2 seconds, then becomes LOW, and WDI is switching to 3.3V voltage every 1 second. At this time, /WDO is kept high.

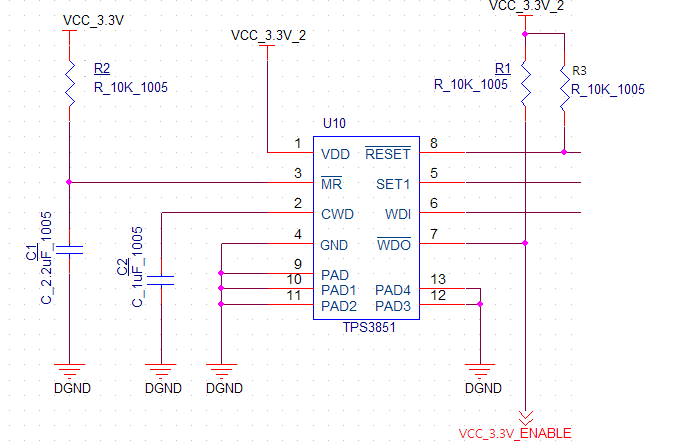

The circuit is roughly as follows.

Thank you.