Other Parts Discussed in Thread: LM5146, LM5069

Hi there

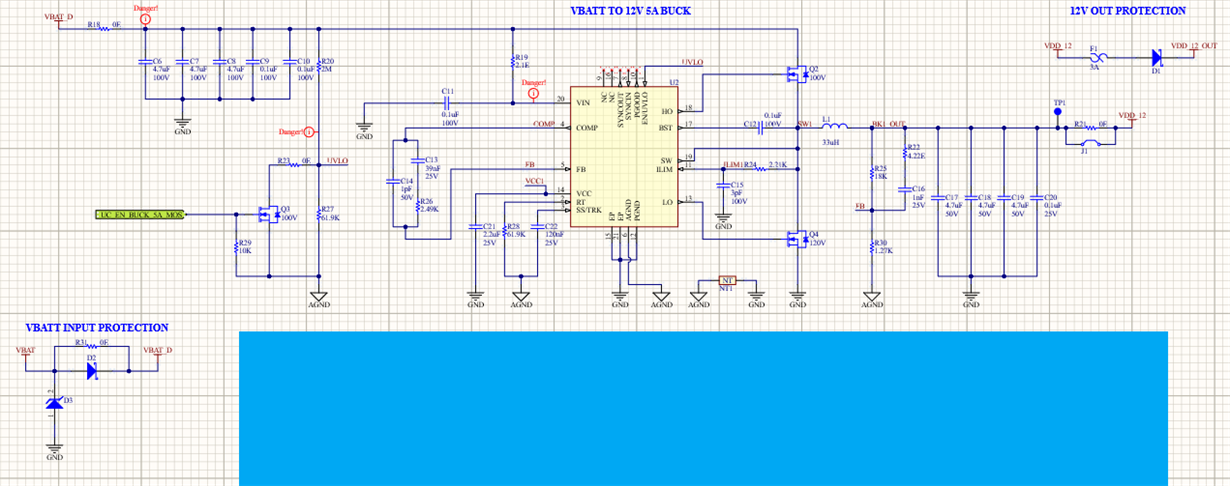

I am facing an issue with the LM5146 buck. I am using it for a 58V to 12V 5A application.

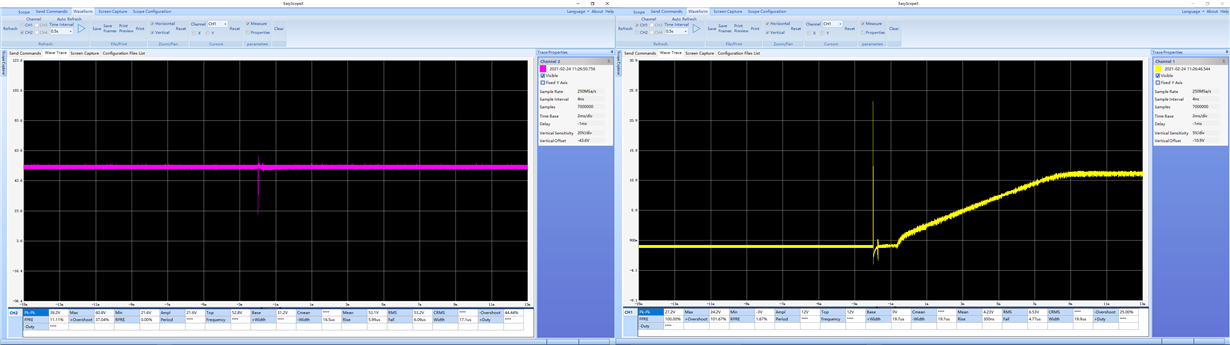

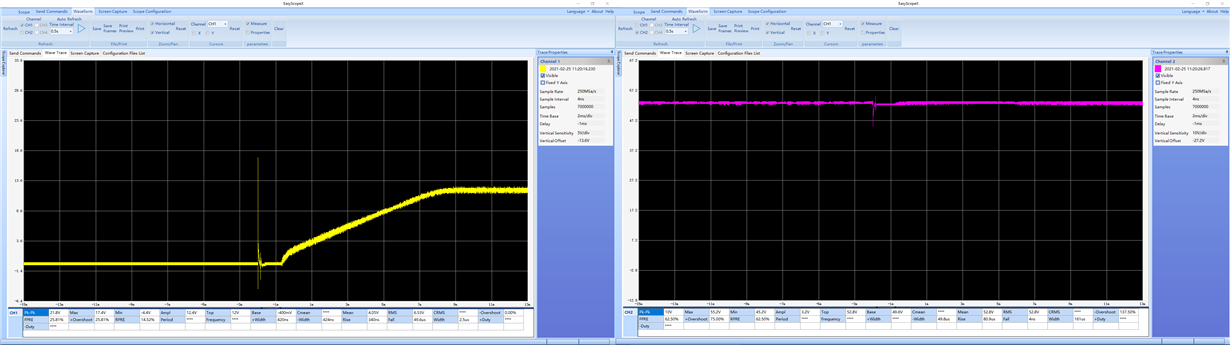

When the input of "58V" is given to the buck through a two pin connector, a huge transience is observed at buck input as well as output. It can be seen in the image attached to this post. The yellow waveform represents buck output and the pink one represents its input.

The input transience ranges from 21.6V to 60.8V and the output transience ranges between -3 to 24.2V.

Kindly help us understand this phenomenon.