Other Parts Discussed in Thread: TPS544C25,

Hi,

Here is an application, the PGOOD pin is pulled up by 105K resistor to BP3 pin from TPS544C25.

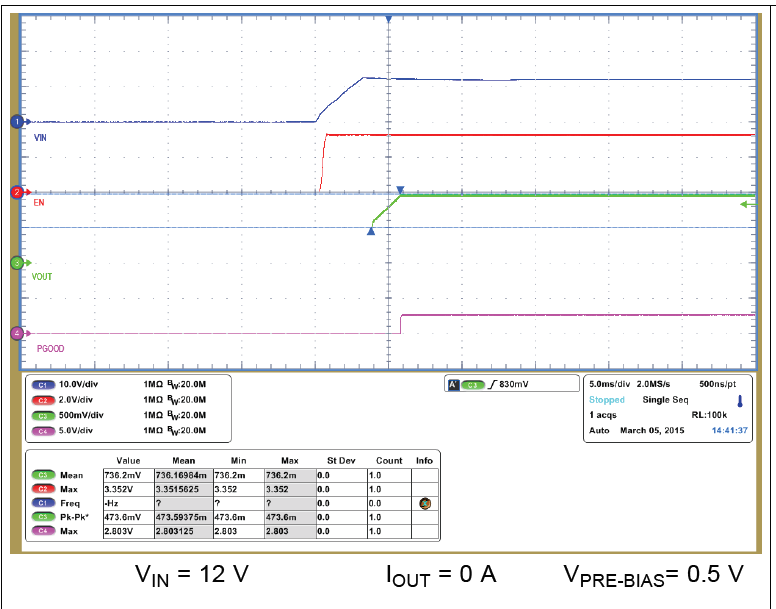

The waveform of EVM in datasheet page 86 is as below(EN is pulled up to BP3), there is no glitch in PG pin.

Here is the questions:

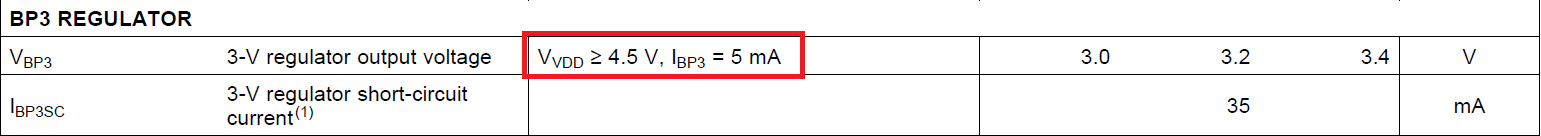

Is there any delay from VDD(4.5V) to BP3(ready to power up)?

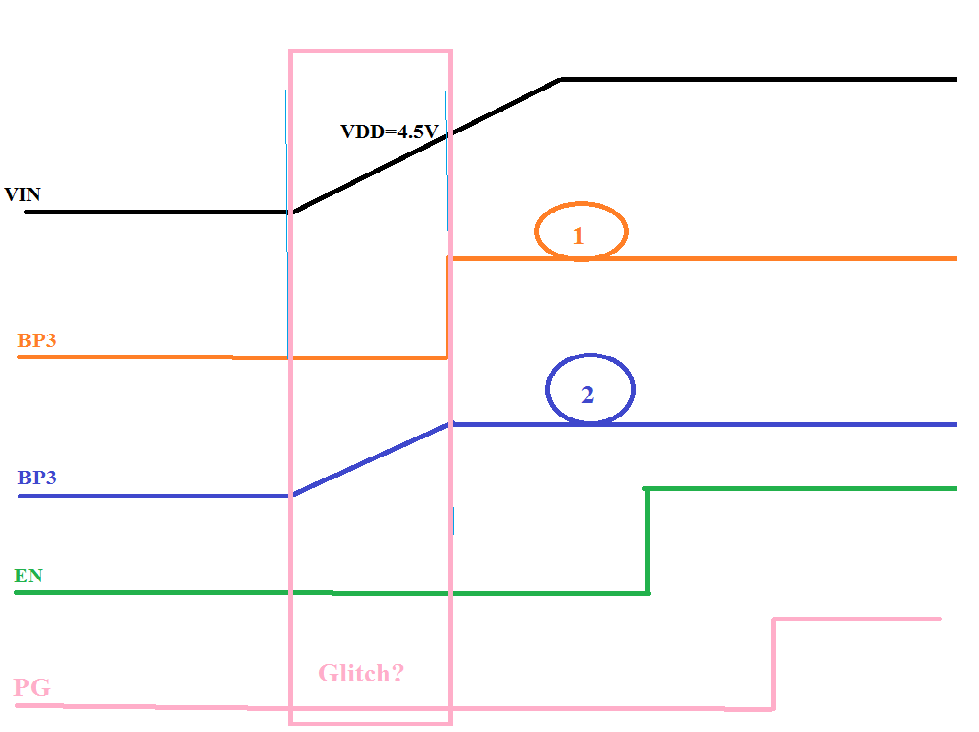

Which curve would be the BP3 looks like in the figure below? 1 or 2?

The concern is when VDD is below 4.5V, will there be any glitch in the PG pin?

Thank you very much.