Other Parts Discussed in Thread: TPS54561

Hi,

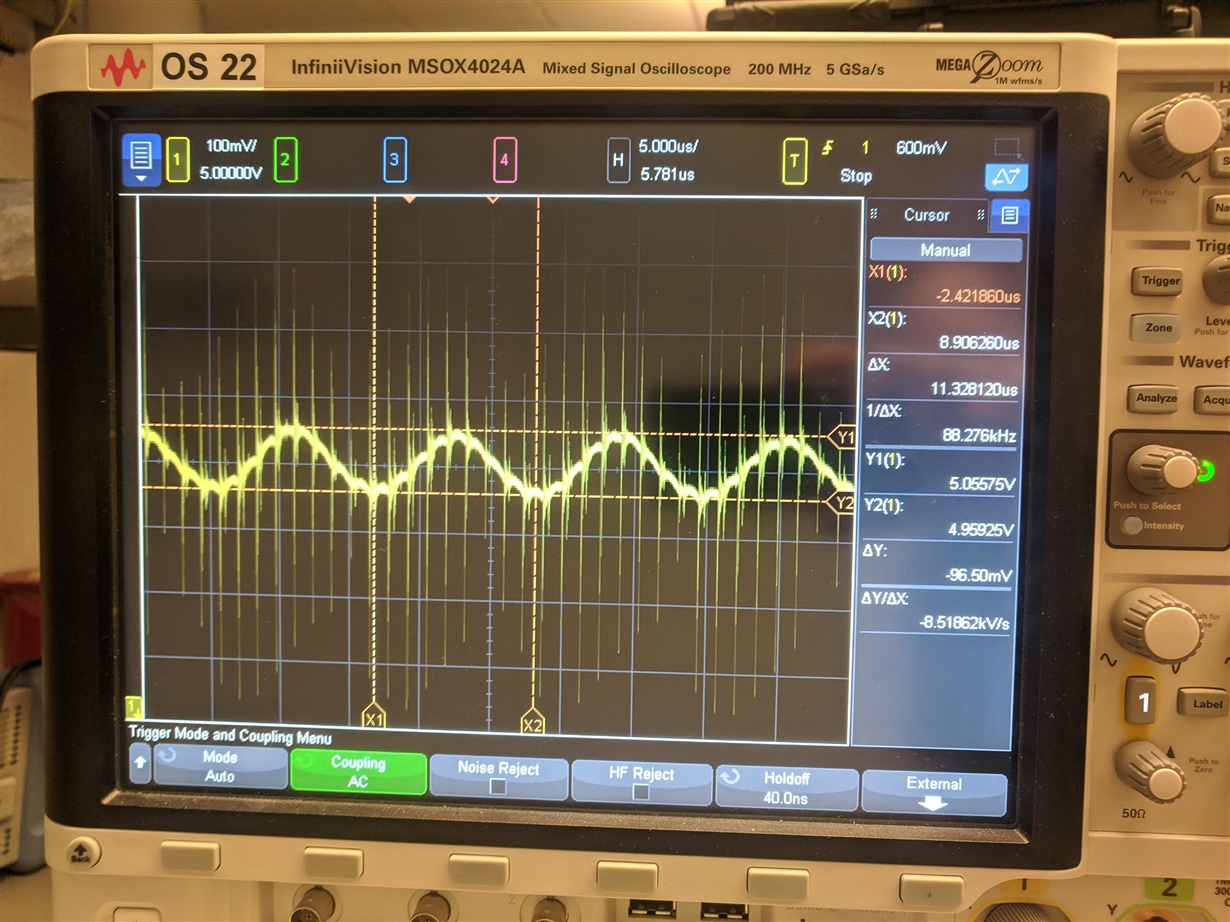

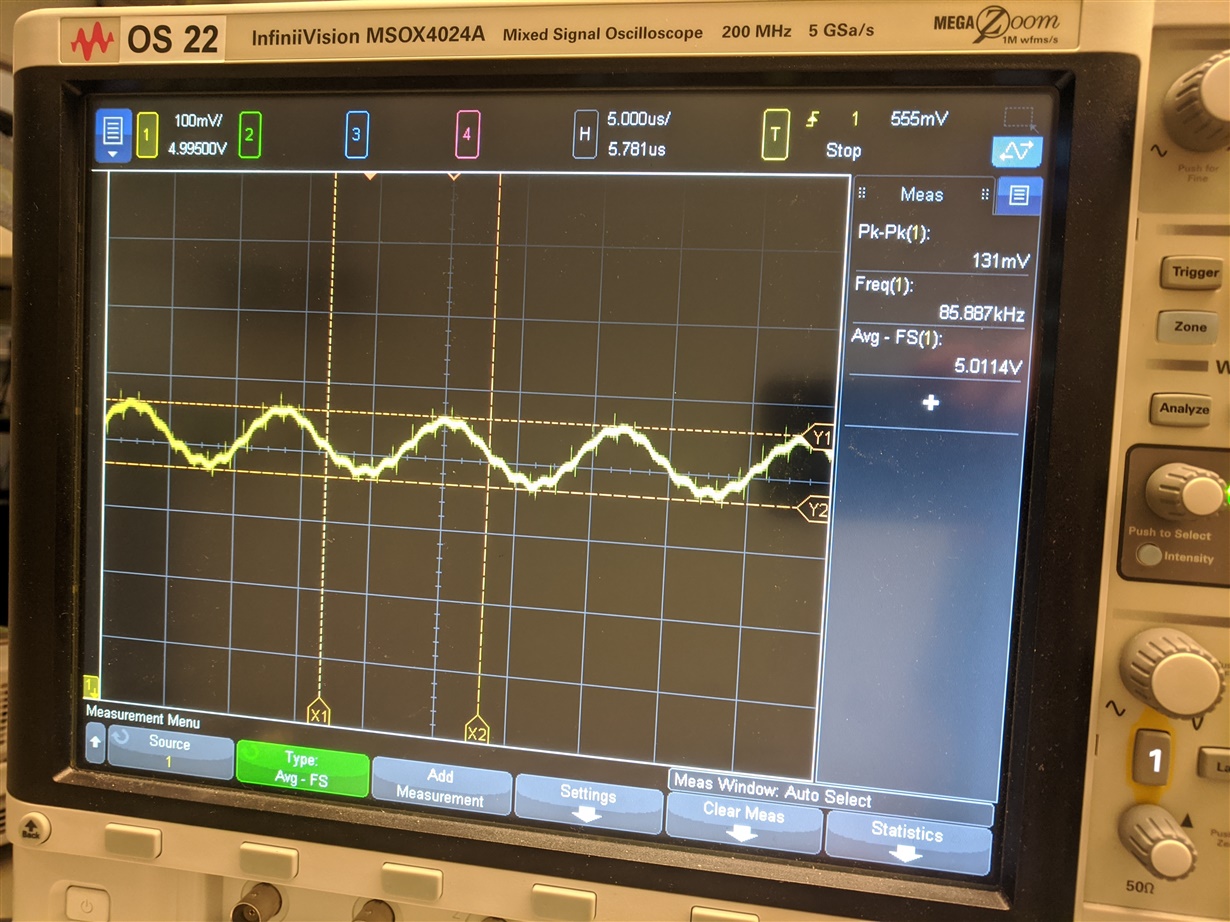

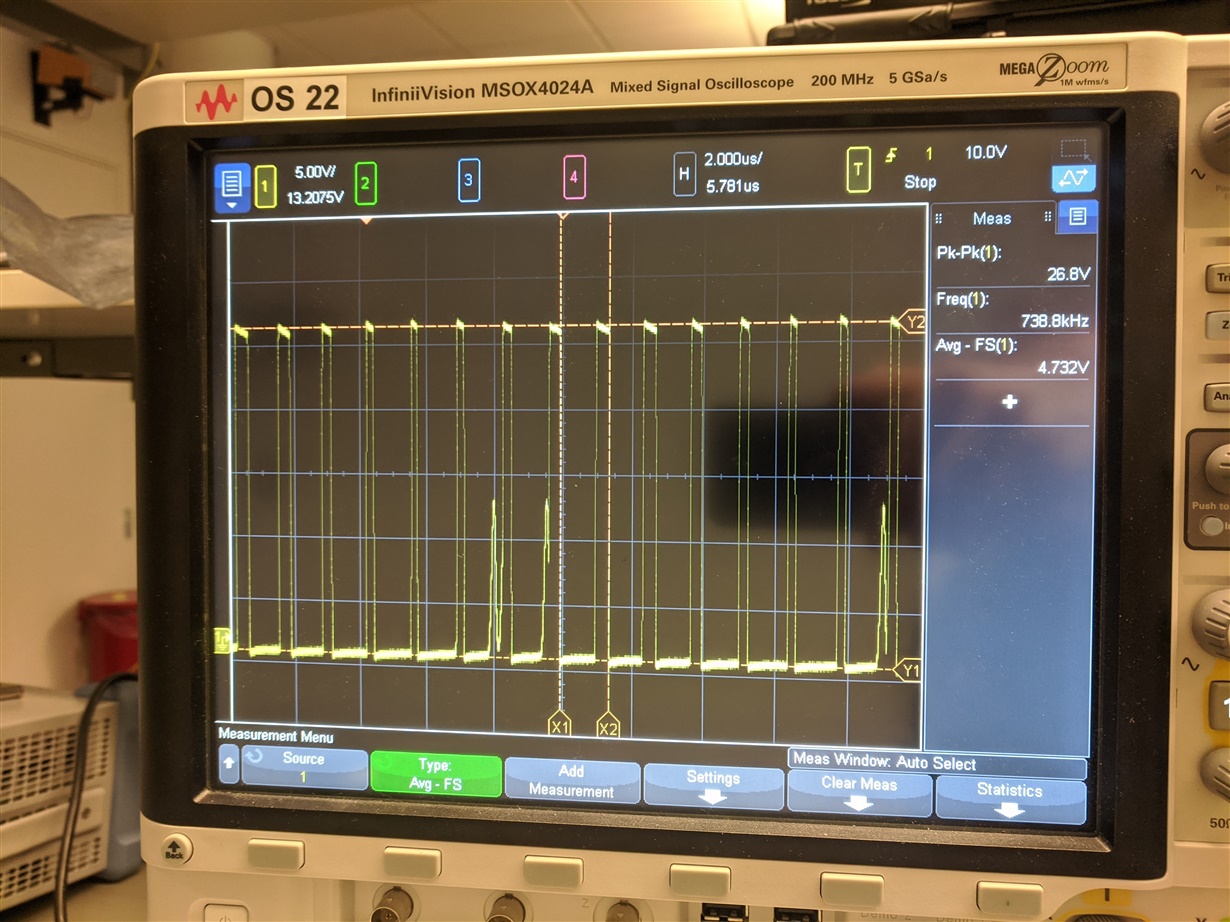

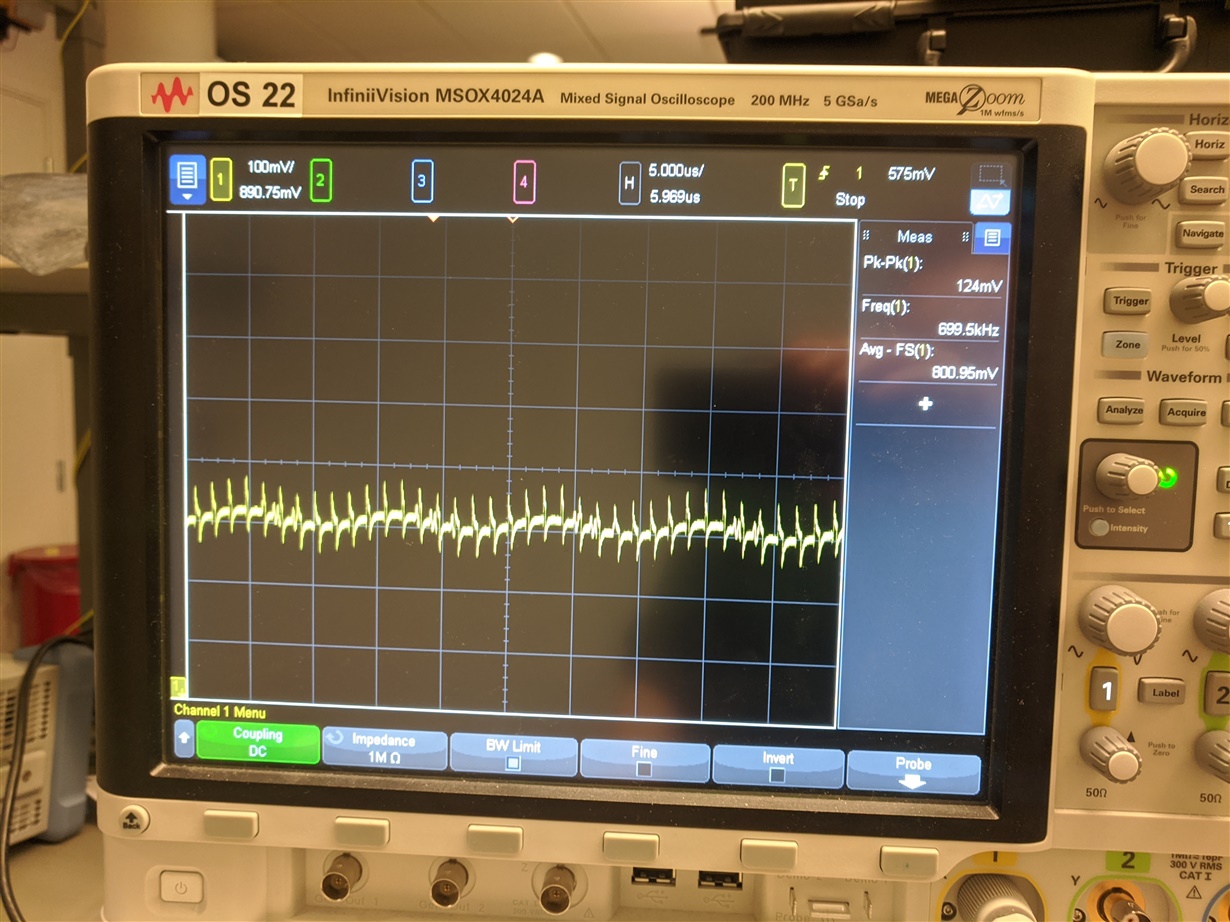

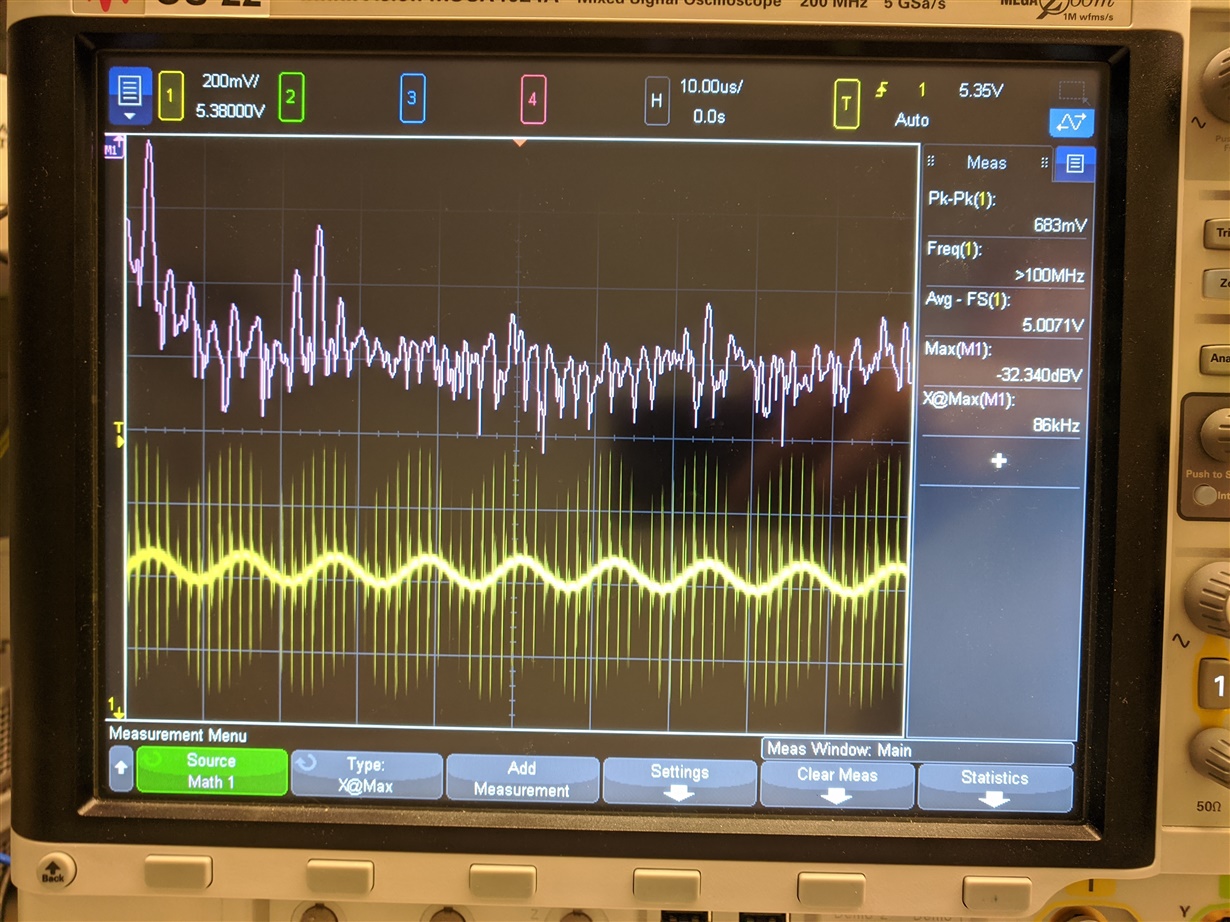

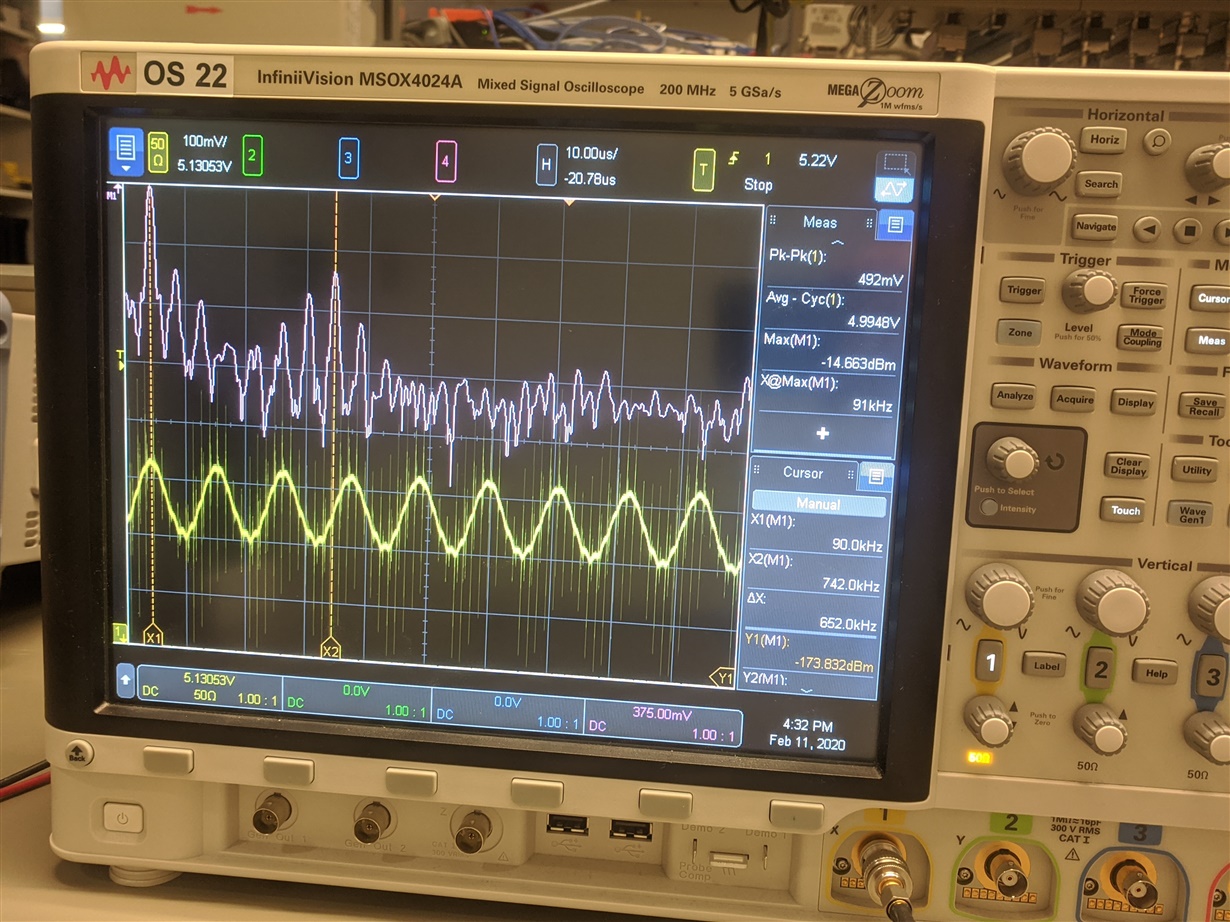

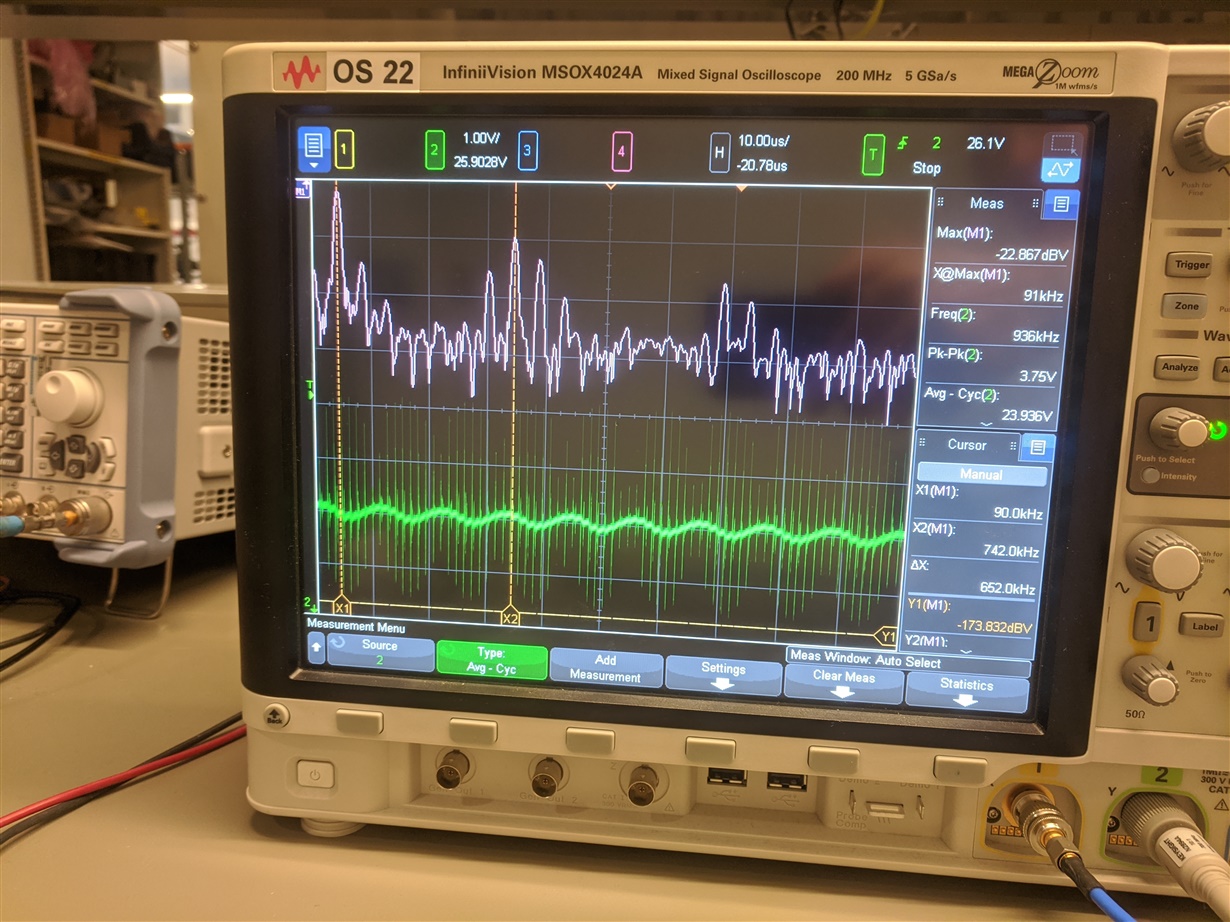

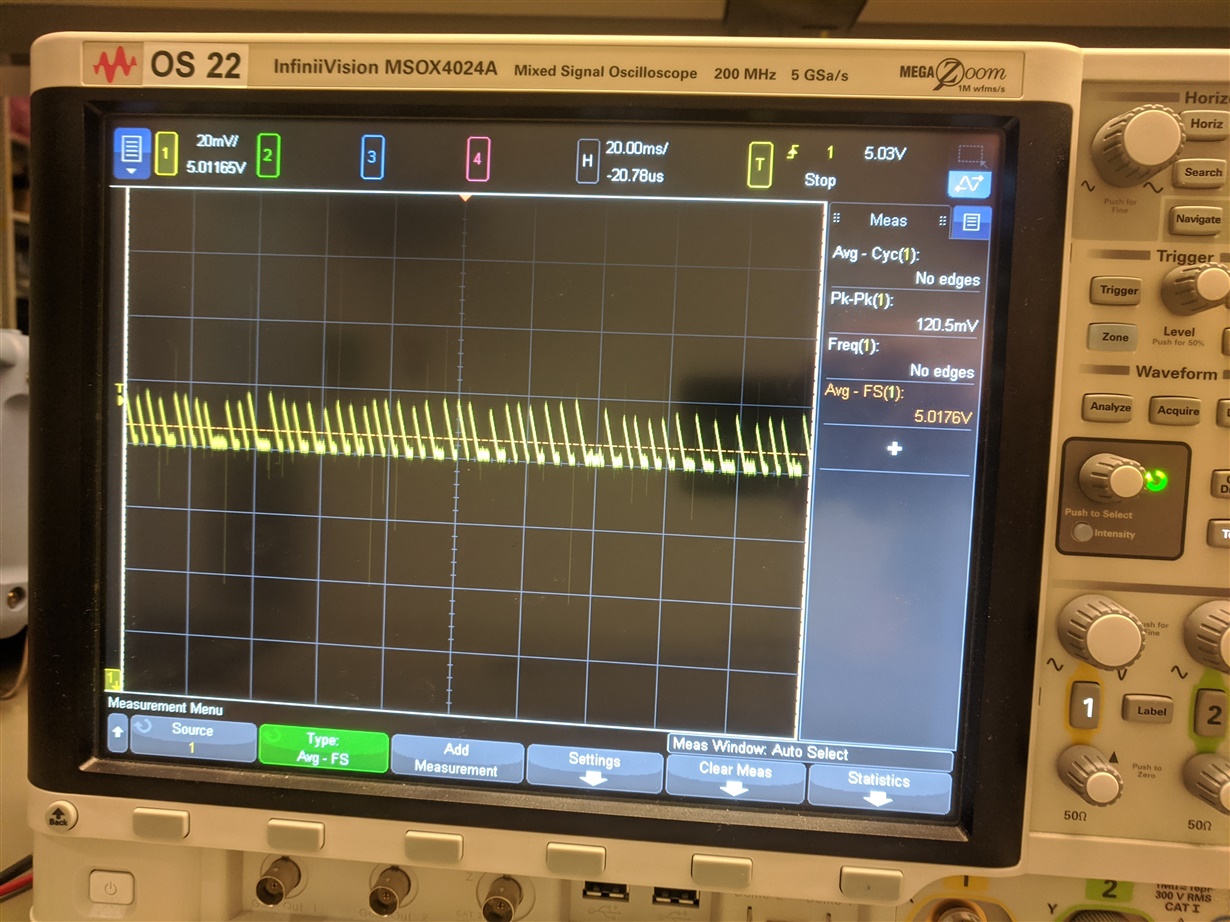

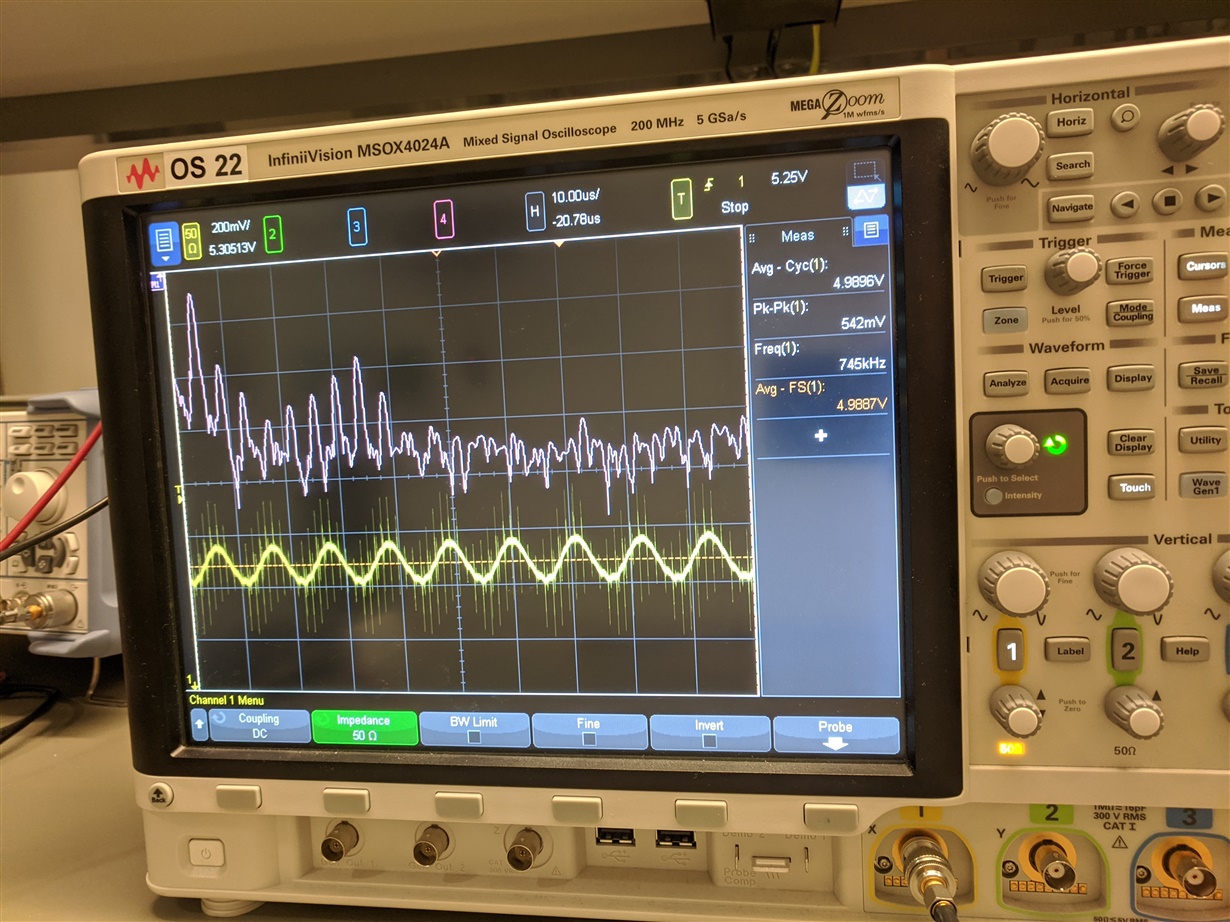

We recently designed a board with the TPS54561 DCDC regulator. The average output voltage is hitting the target of 5V, however we see a switching noise on top of it, with peak-to-peak value of between 500mV and 800mV. This is well above the simulated noise level of 34mV peak-to-peak. This ripple is at the same frequency as the expected switching frequency of the regulator (737 kHz).

The board is a 10-layer board, with several DCDCs connected in parallel at the TPS's output for further regulation to 3V3 and 1V8. With a power resistor load instead of these DCDCs, the ripple reduces to 400mV peak-to-peak. The regulator typically regulates from a Vin of 24V. We also see this 737kHz switching noise on the input - but then 5V peak-to-peak.

Do you have any suggestion what might be the reason for the noise, and how to correct the circuit to remove it?

So far we see the following possible culprits:

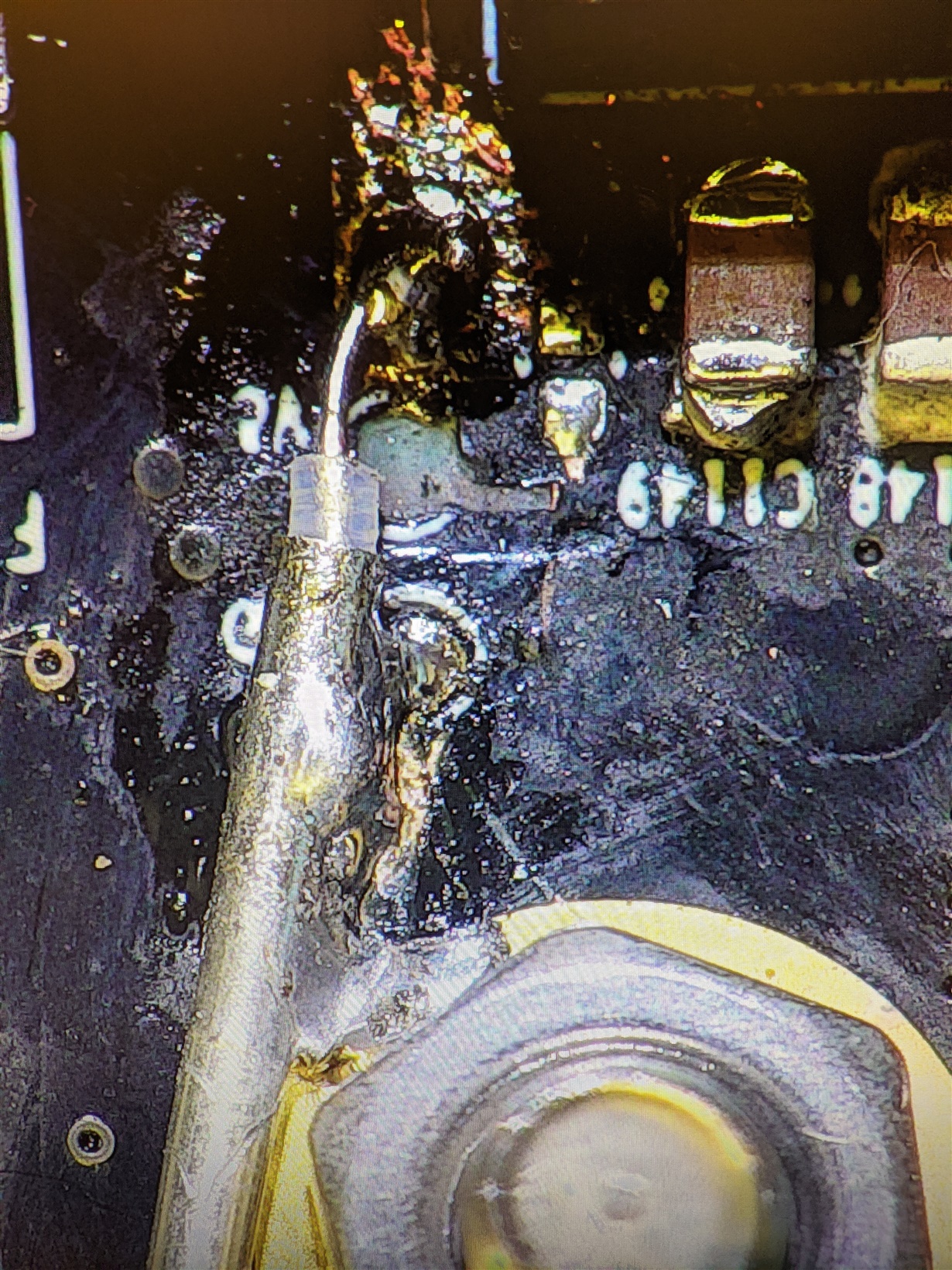

• Lack of ground plane on closest layer underneath TPS IC – next ground plane below chip is on layer 5. There is a ground plane on adjacent layer underneath the larger power connectors (seen as mounting holes in the upper part of the layout snippet).

• Lack of ground vias on DCDC chip's thermal pad

Best regards,

Jonas

Design information

- Webench: https://webench.ti.com/appinfo/webench/scripts/SDP.cgi?ID=6EFD740ECFF3856D

- Schematics: tps54561-schematic.pdf

- Layout: