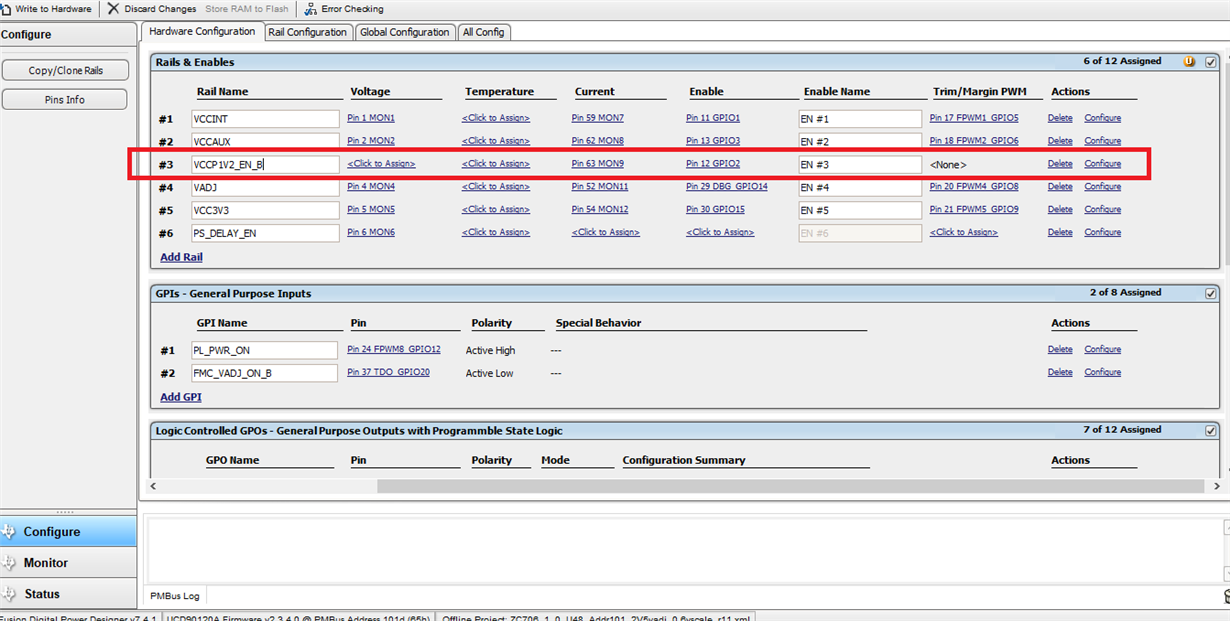

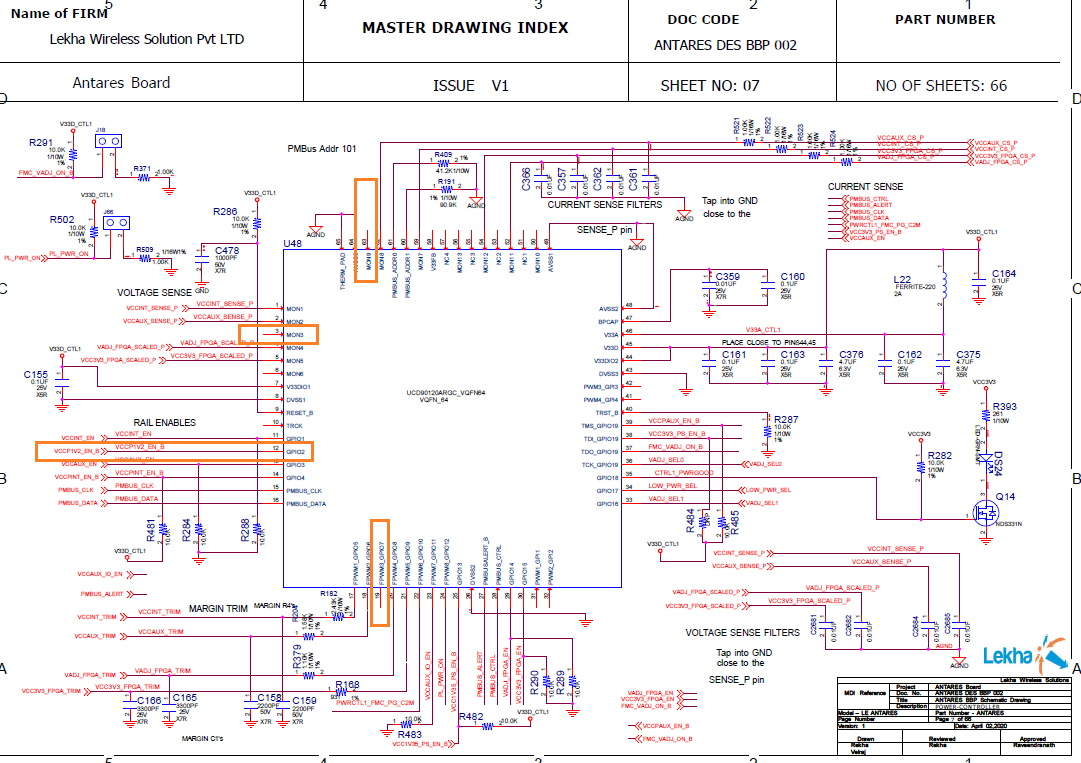

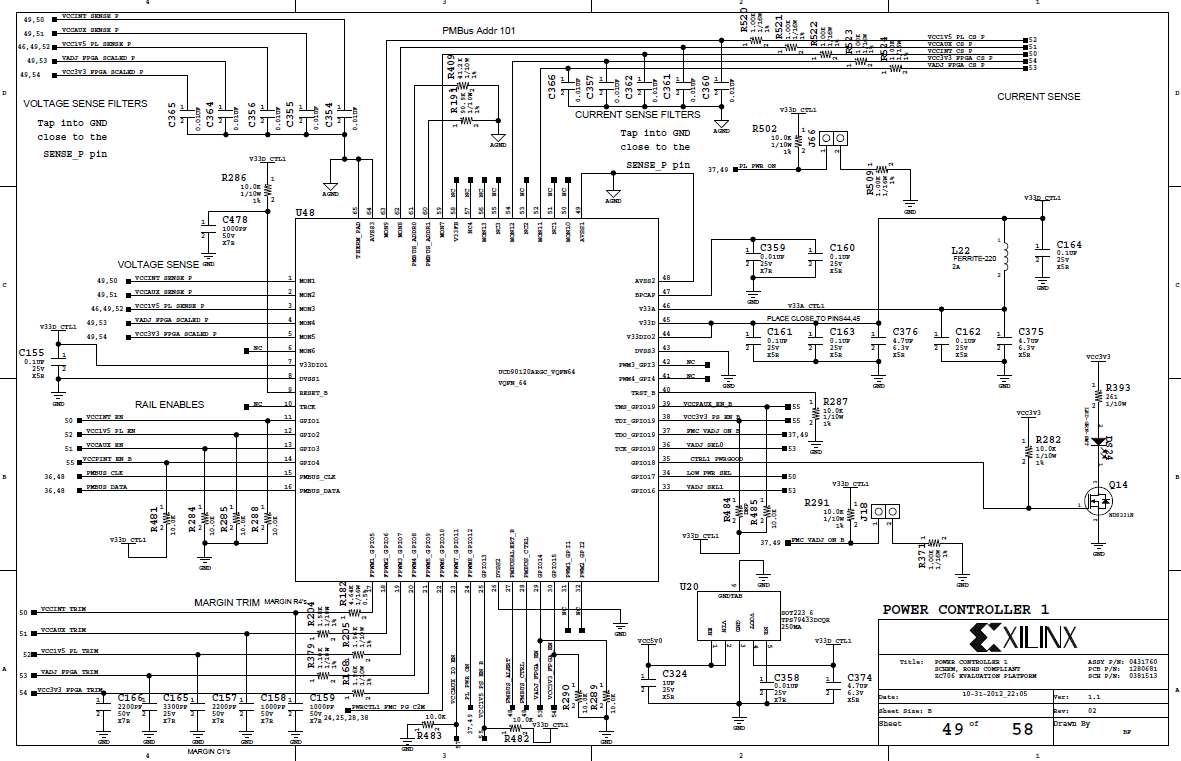

All the power enabling, controlling, monitoring are same as ZC706 development kit except there is changes in the Enable pins at GPIO2 (attached snap shot of the same),

for GPIO2 (power on sequence is same for VCCP1V2_EN_B as VCC1V5_PL_EN) disconnected MON3, MON9 and FPWM3_GPIO7 signals. I have imported ZC706 .xml file and made changes as shown in the Fusion digital power designer(I have removed voltage, trim/margin and current for the GPIO 2 based signals).