I'm testing a small batch of boards with LM5163 as voltage inverting buck regulator; these are the design specifications:

Vout=-17V

Vin(min)=36V (ie:18V+17Vout)

Vin(nom)=65V (ie:48V+17Vout)

Max output current= 150mA (70mA nominal with derating due to added safety margin and inverting configuration)

Switching frequency=320kHz

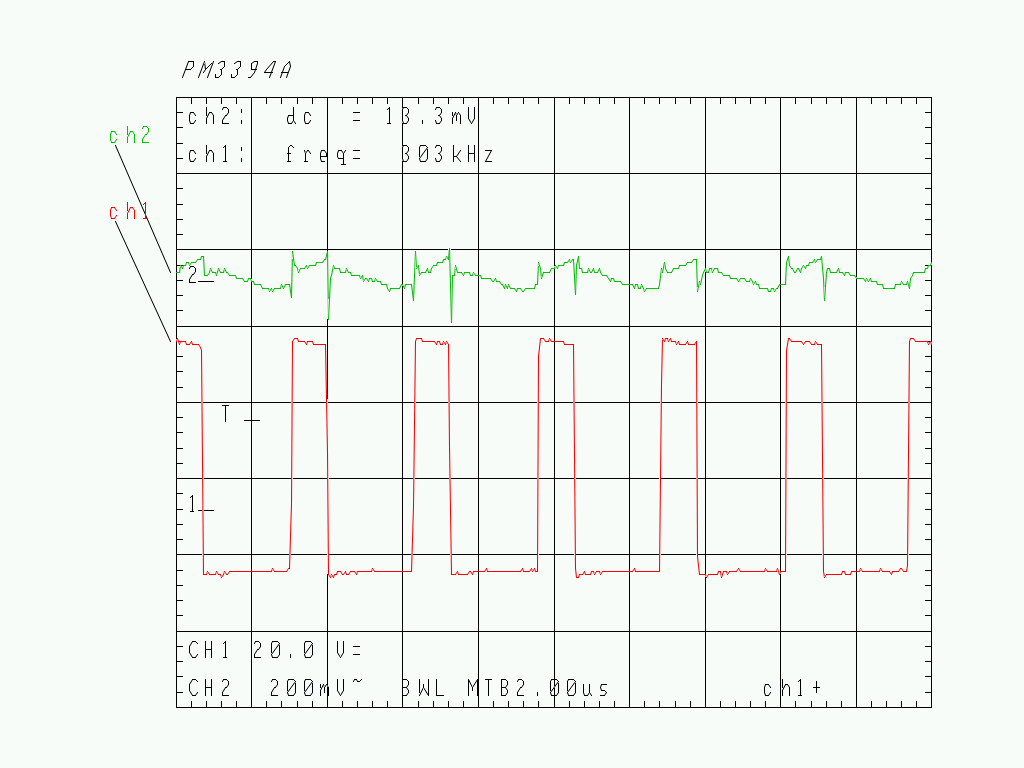

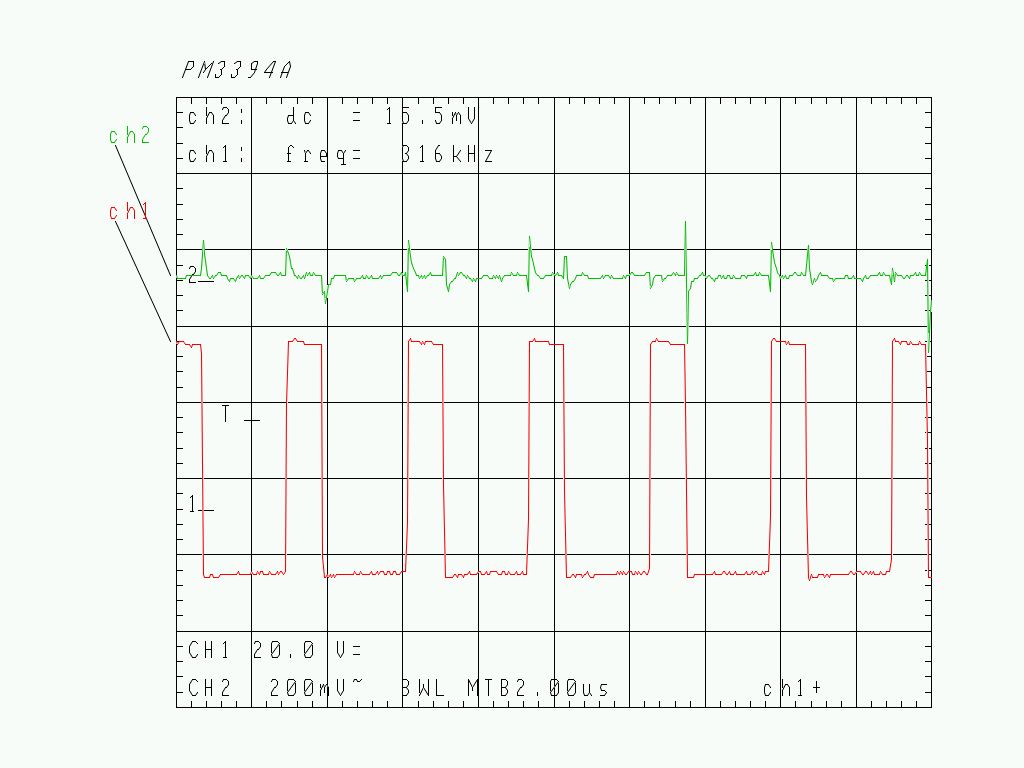

Actual input voltage is +48V and output voltage is -17V @60mA load current.

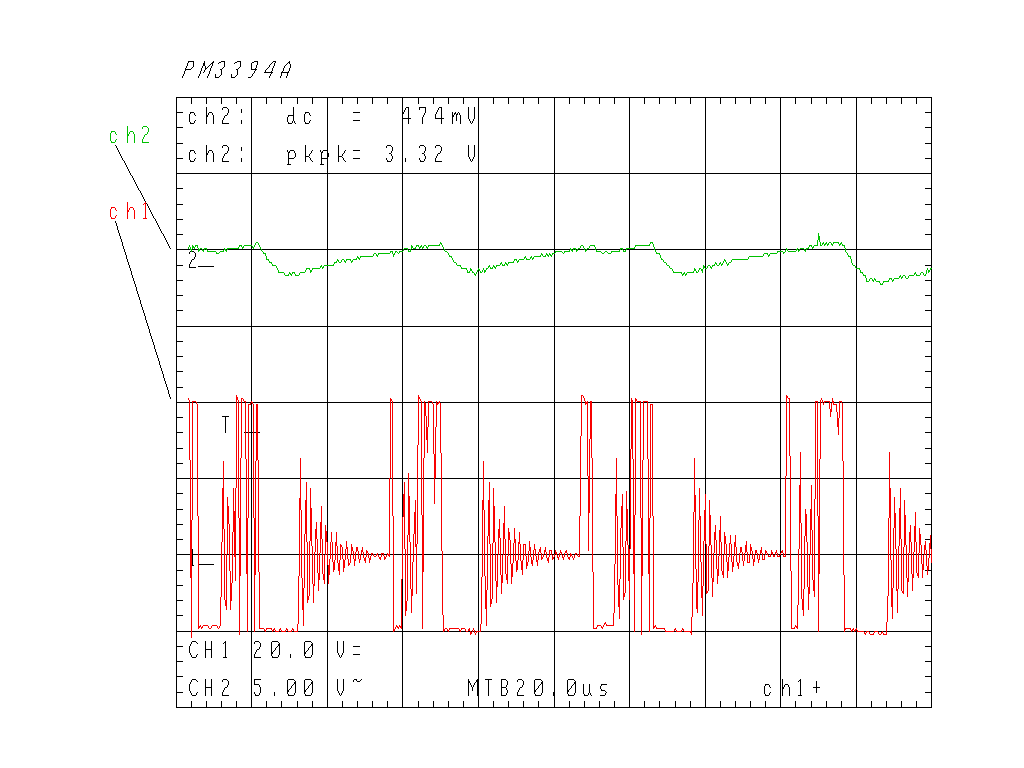

My concern is the output voltage with a superimposed ripple of 2Vpk-pk in the 8-10kHz frequency range. I think the controller is failing to enter CCM, or something is eating up too much phase margin leading to control loop instability. Also the inductor (Bourns SRR1260-391K from Mouser) is generating some audible "hissing" noise.

Where am I wrong?

I've read some topics about this controller in this forum, mainly around "type 3" configuration details; is LM5163 supposed to work properly in "type 2" ripple feedback circuit?

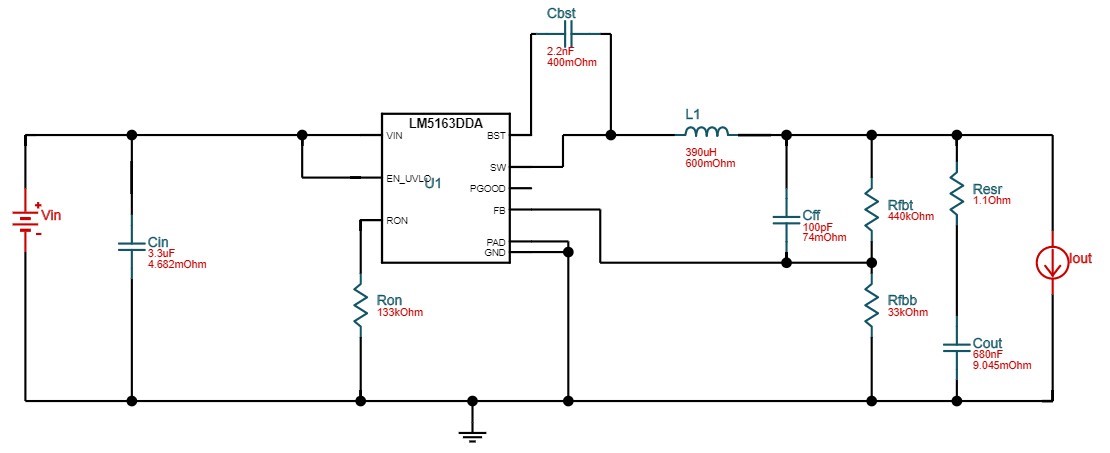

This is Webench design:

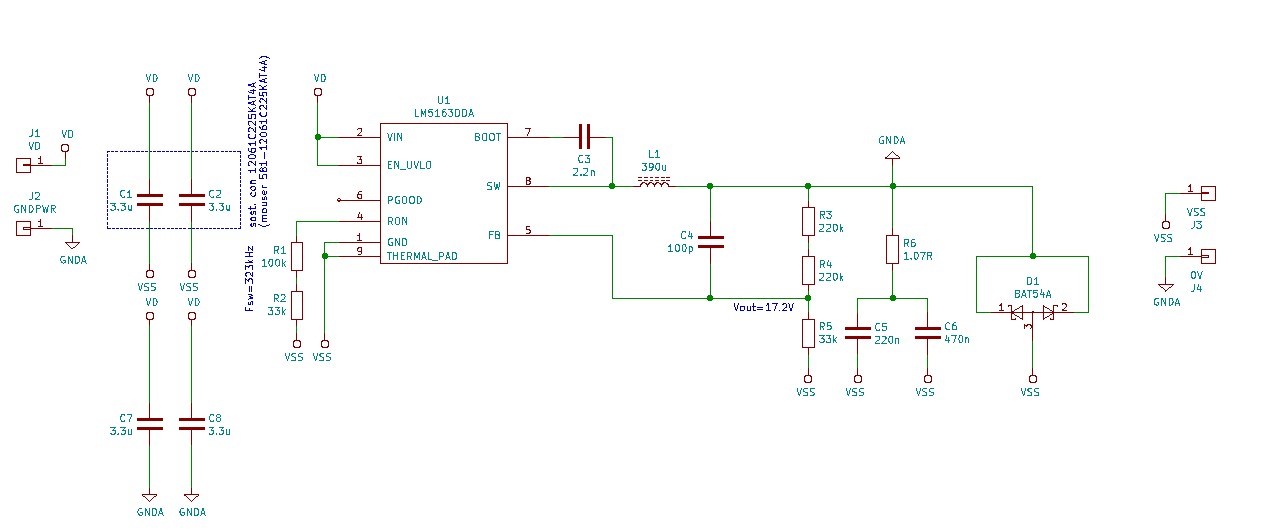

This is the actual circuit: