Other Parts Discussed in Thread: CSD87381P

Hi All,

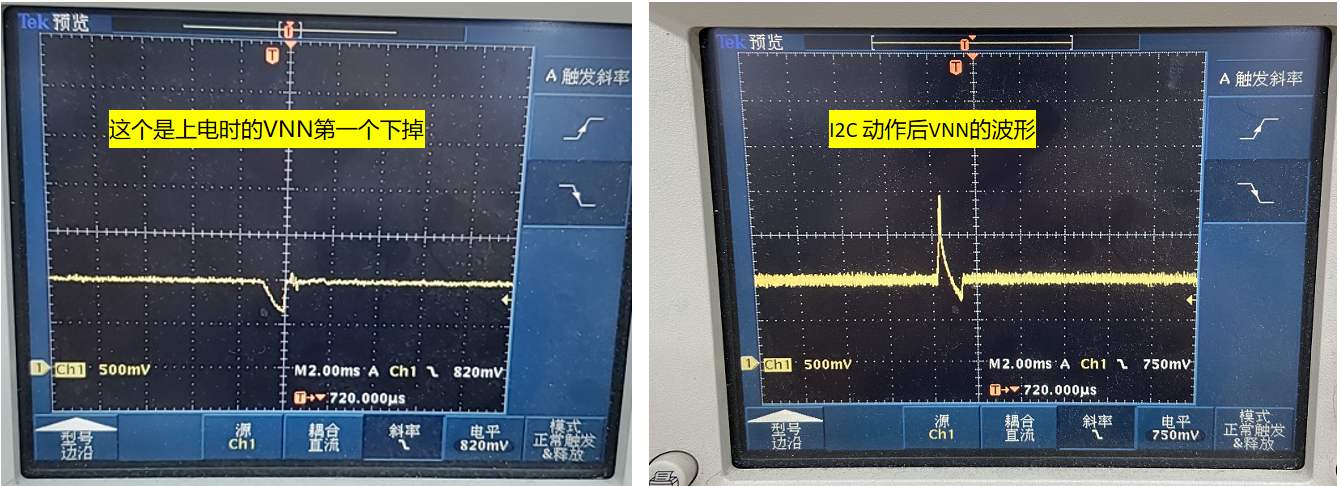

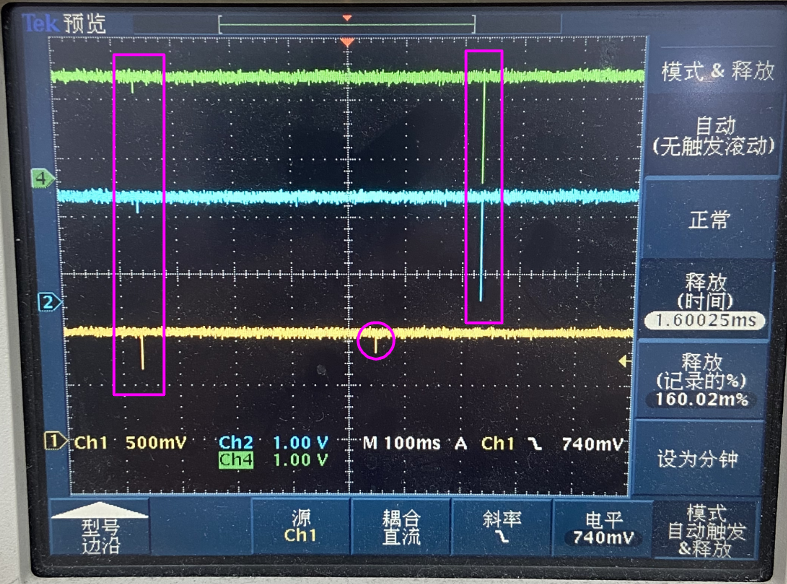

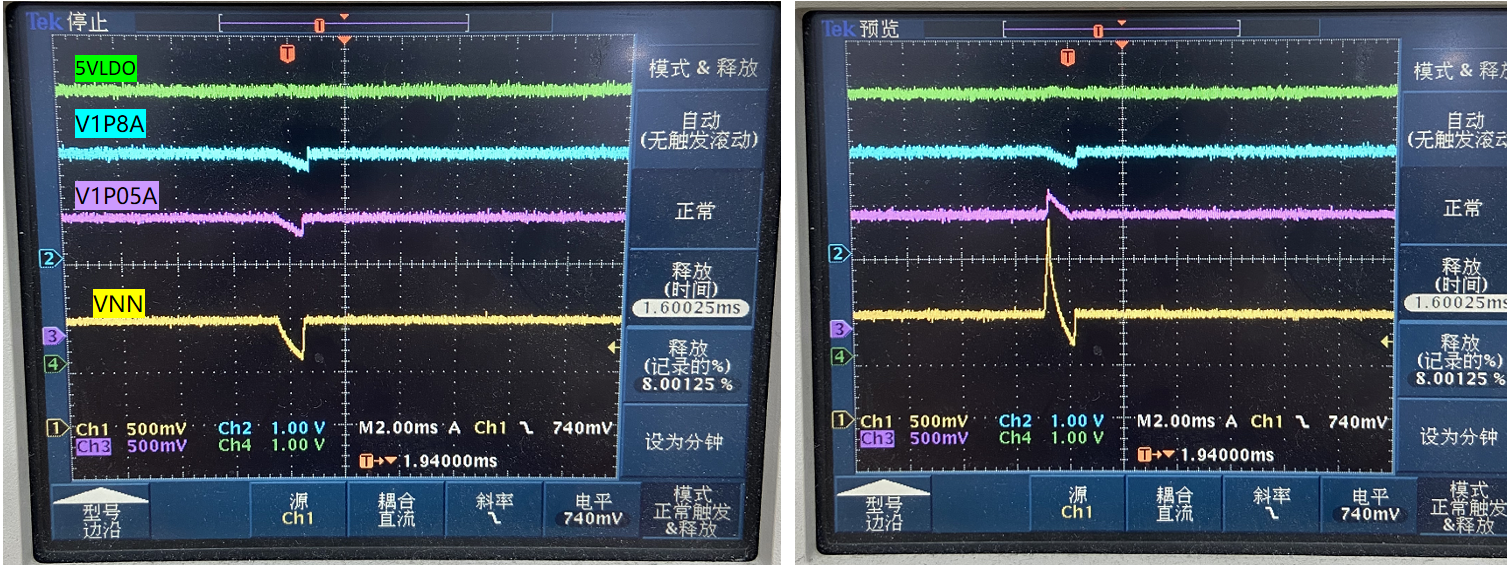

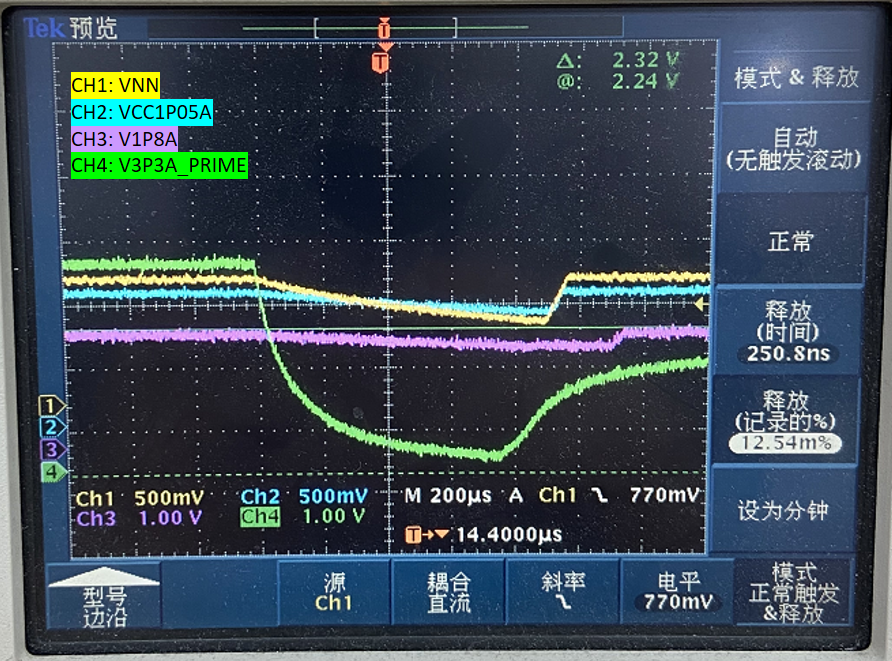

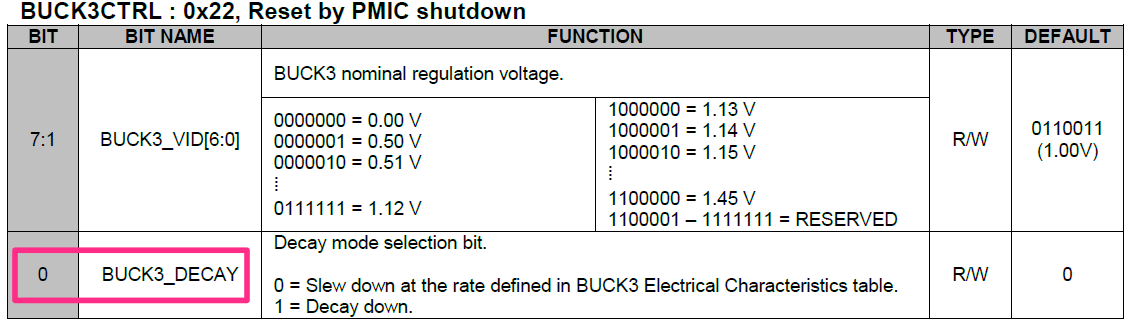

One of our projects uses the TPS650842 PMIC product. When powering on, a voltage drop occurred in VNN (Buck3) , which will cause power down later.

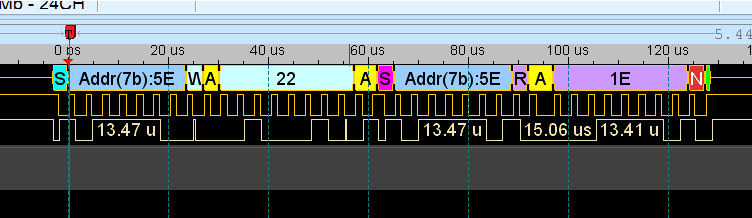

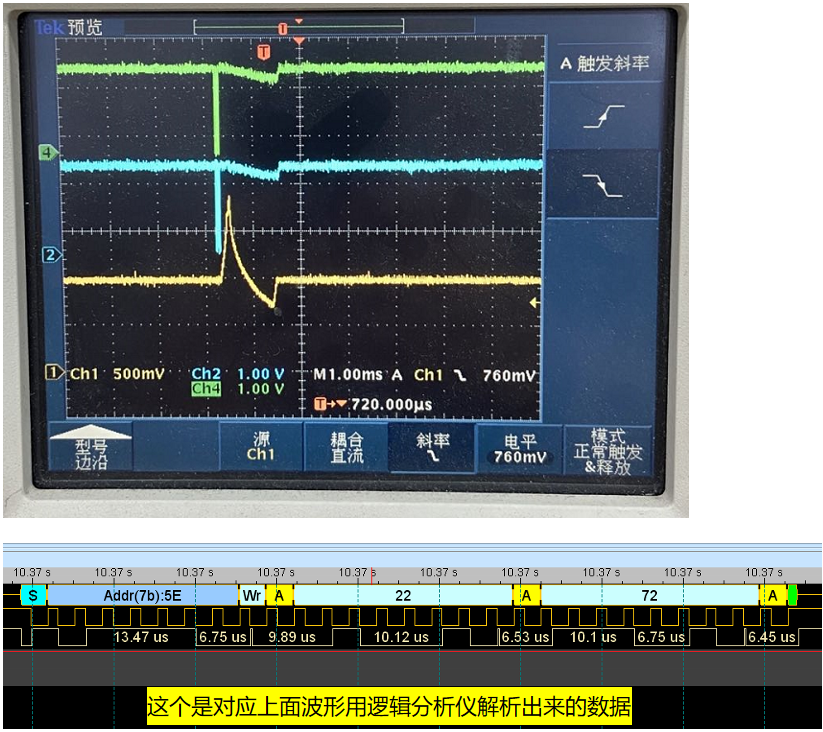

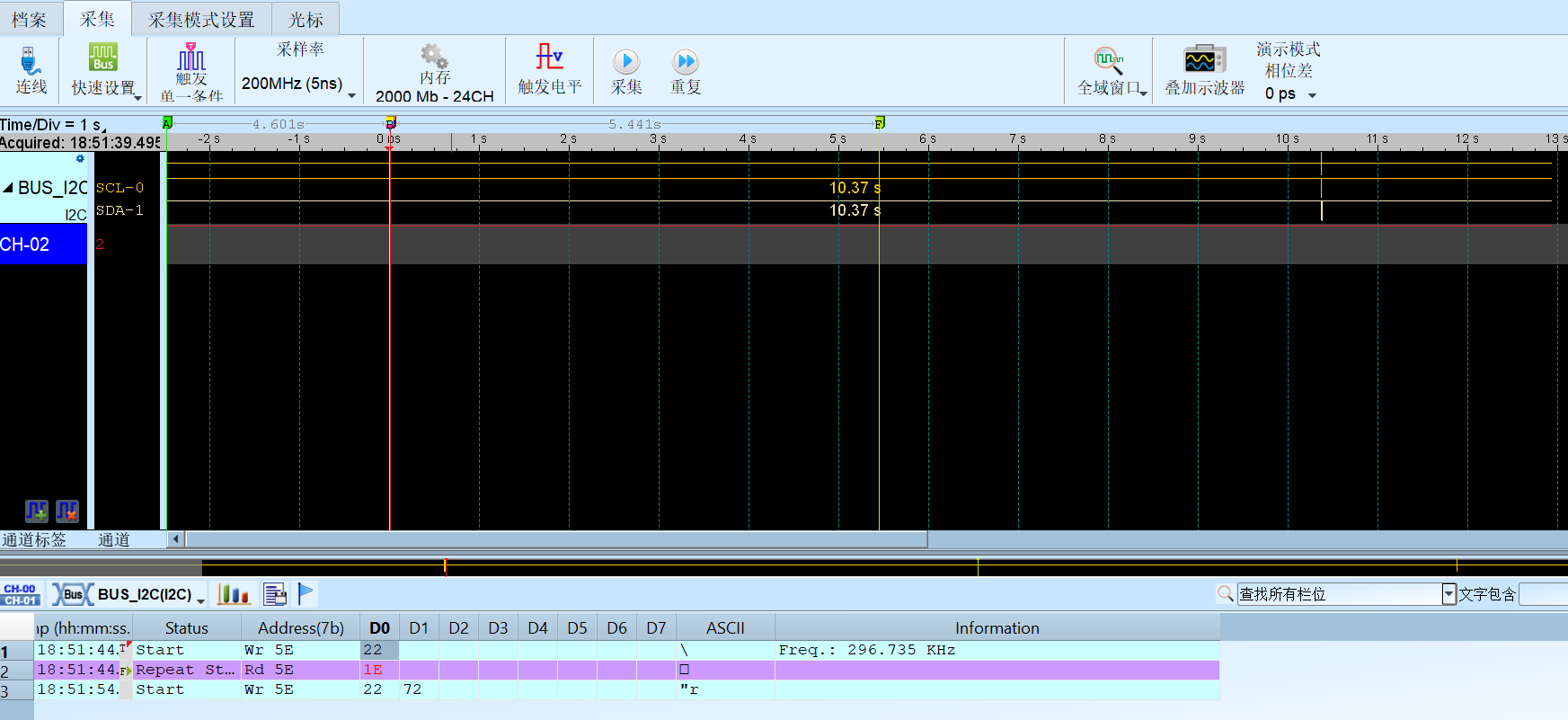

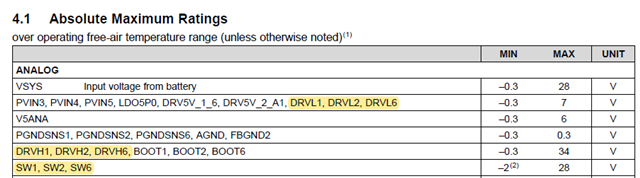

We have read this voltage drop through I2C, and then try to adjust the VNN voltage, but the VNN voltage will eventually reach about 1.8V (the specification shows that VNN voltage is 1.05V@typ. and 1.45V@max.), then the system is powered off.

Can u help to analyze the reason for this problem? I added the schematic diagram of my circuit design and the drop waveform to the below.

Thanks,

Best Regards

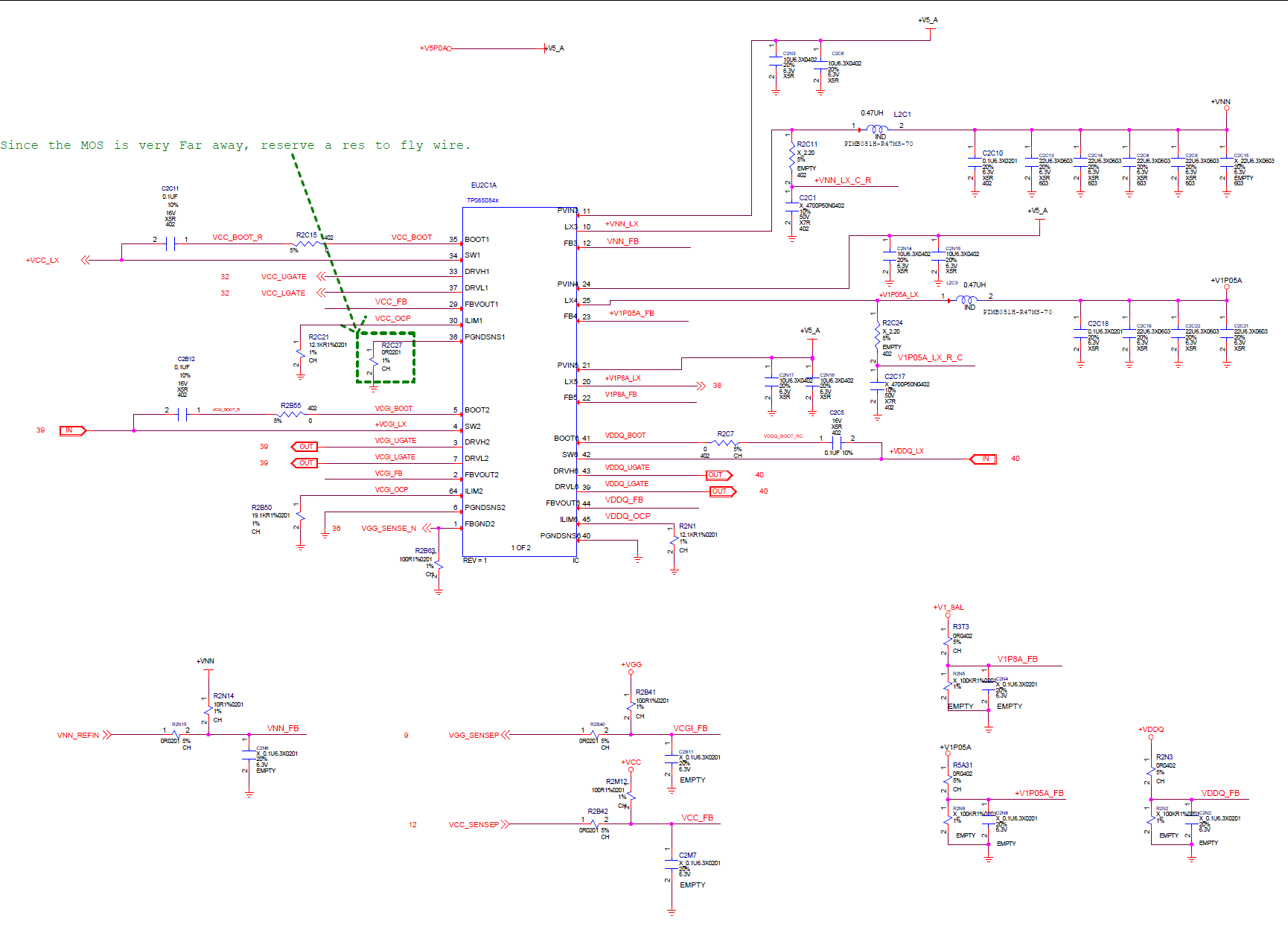

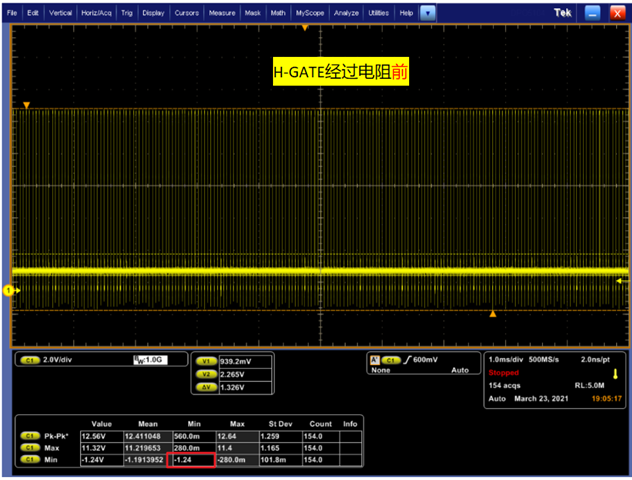

Schematic diagram:

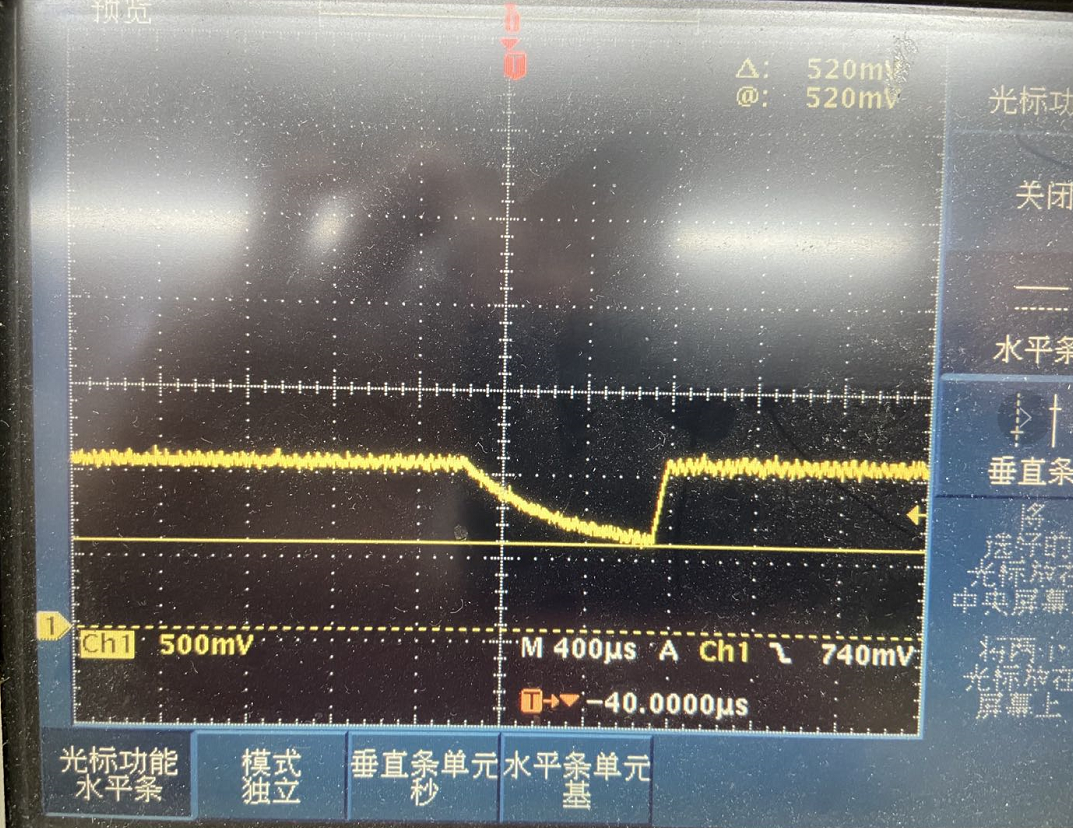

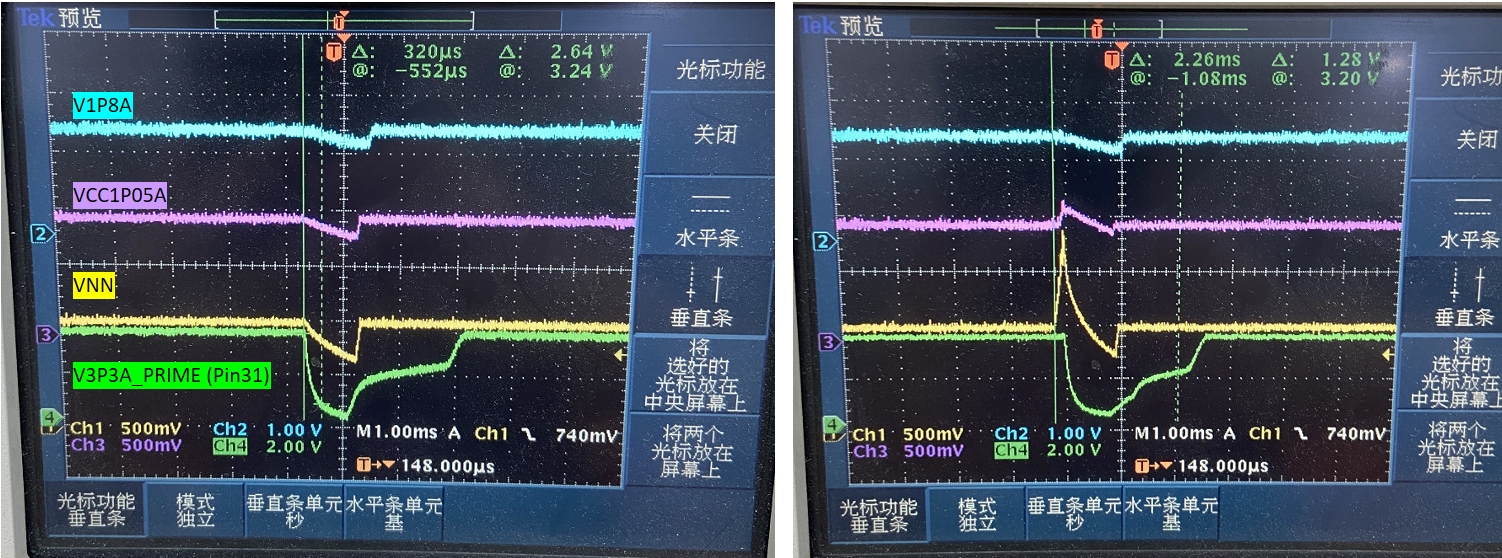

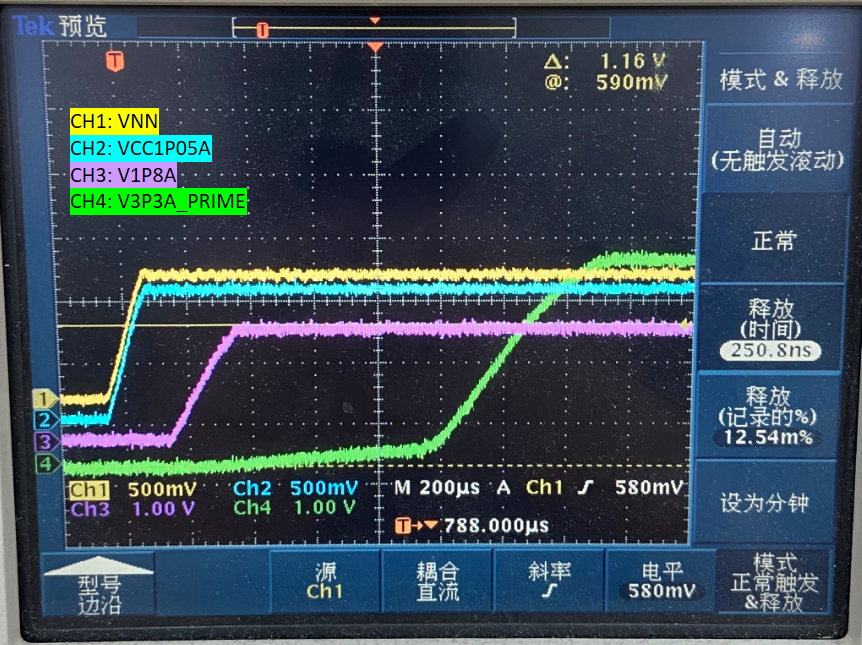

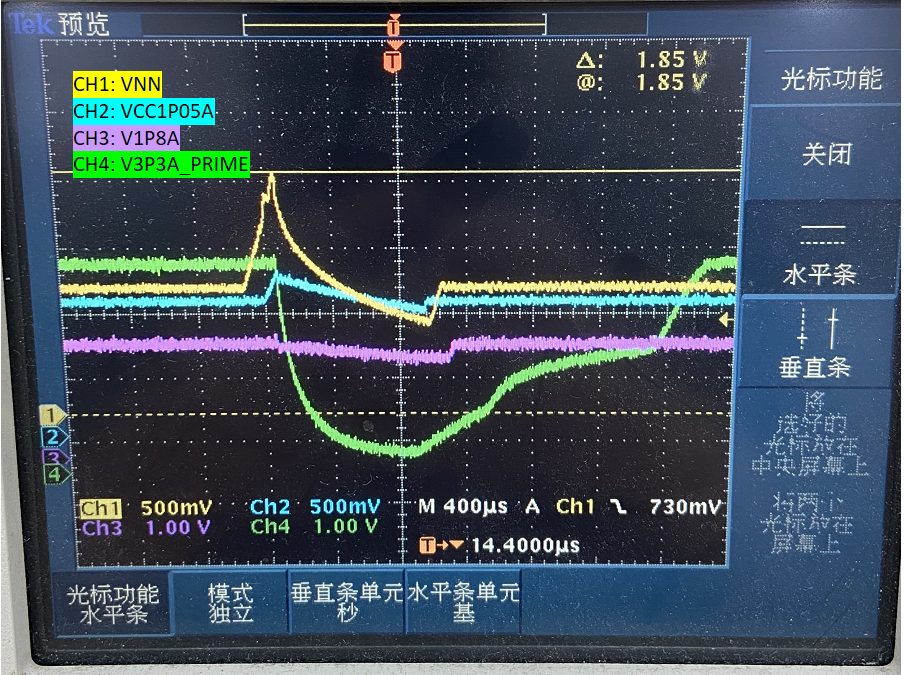

Drop waveform: