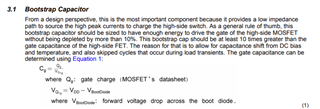

Other Parts Discussed in Thread: SN6501, UCC27282

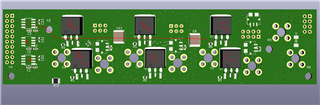

I have designed a power stage 3-phase driver card using the UCC27211 as the gate driver. I have tested the setup in a controlled environment using a function generator at 3.3V levels to drive the gate LI / HI inputs of the UCC27211. From my oscilloscope experiments, I can see that only the low-side gate is being activated by the device. The high side is not driving the high side MOSFET gate. Is there some issue with the bootstrap circuit? I didn't find much recommendation for bootstrap circuitry in the device datasheet, but all I have done is experiment with different values of bootstrap capacitors, with no success. The MOSFETs I am using (IPB072N15N3GATMA1) have a gate charge of approximately 70 nC, for reference. I have posted the schematic here for reference. Any advice on debugging this and figuring out why the high side drive is not working as expected?