Hi support team:

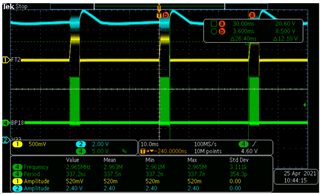

I am tested Hiccup status, in my understand if output current more than 13.8A, system well trigger hiccup mode so l had test this situation. the test waveform as follow.

In my test, hiccup wait time is 26.7ms? l don't know it reason?

in addition: why output rise time has 6ms? the soft-start time just 1ms