Tool/software: Code Composer Studio

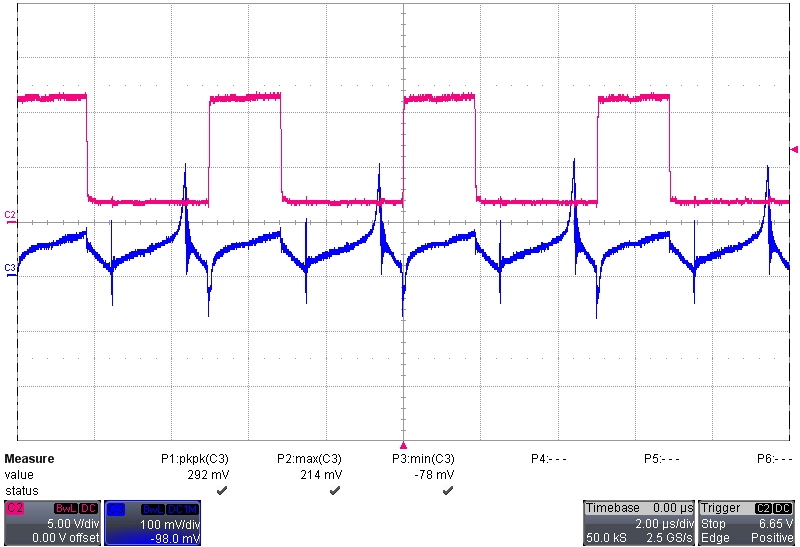

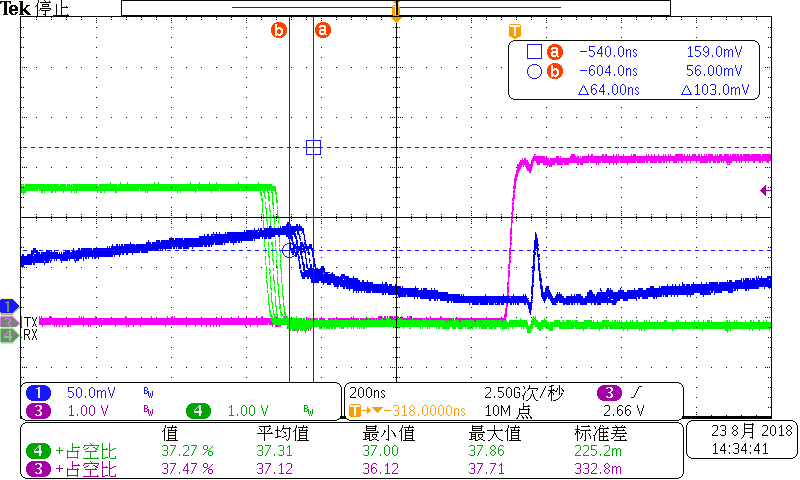

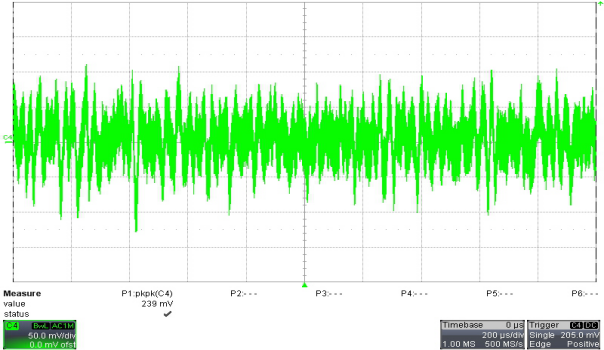

The loop control mode is PCM. After test, find that the PWM output duty have shake. I want to know that the shake is come from voltage loop or current loop. How can i debug?

The front end2 DAC connect the filter0 output. And i output the data of FILTERXNREAD,DPWMFILTERDUTYREAD and find that the data also shake. So maybe the shake come form voltage loop.

Then I set the front end2 DAC connet DAC0 and set the DAC0 as follow:

LoopMuxRegs.EXTDACCTRL.bit.DAC2_SEL = 0;

voltage.ref = vout_cali;

voltage.dac_value = voltage.ref;

FeCtrl0Regs.EADCDAC.bit.DAC_VALUE = voltage.dac_value;

Is the code which i write right? if wrong, how can i get the useful register information for the issue??

Thanks!