Other Parts Discussed in Thread: UCC28061,

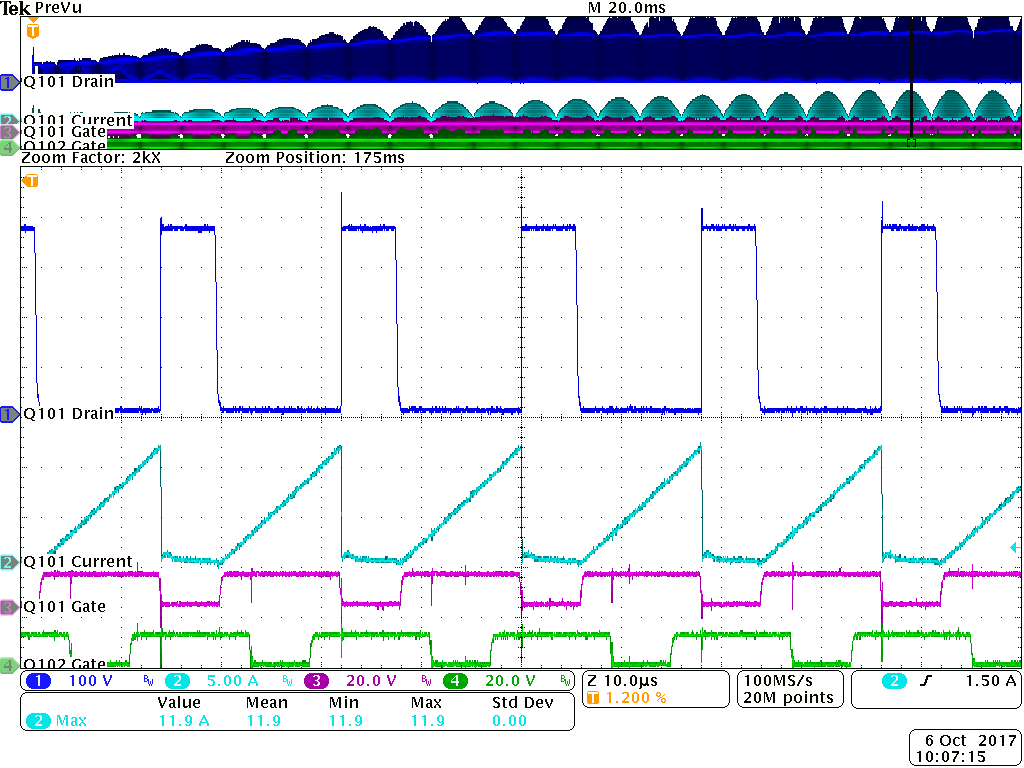

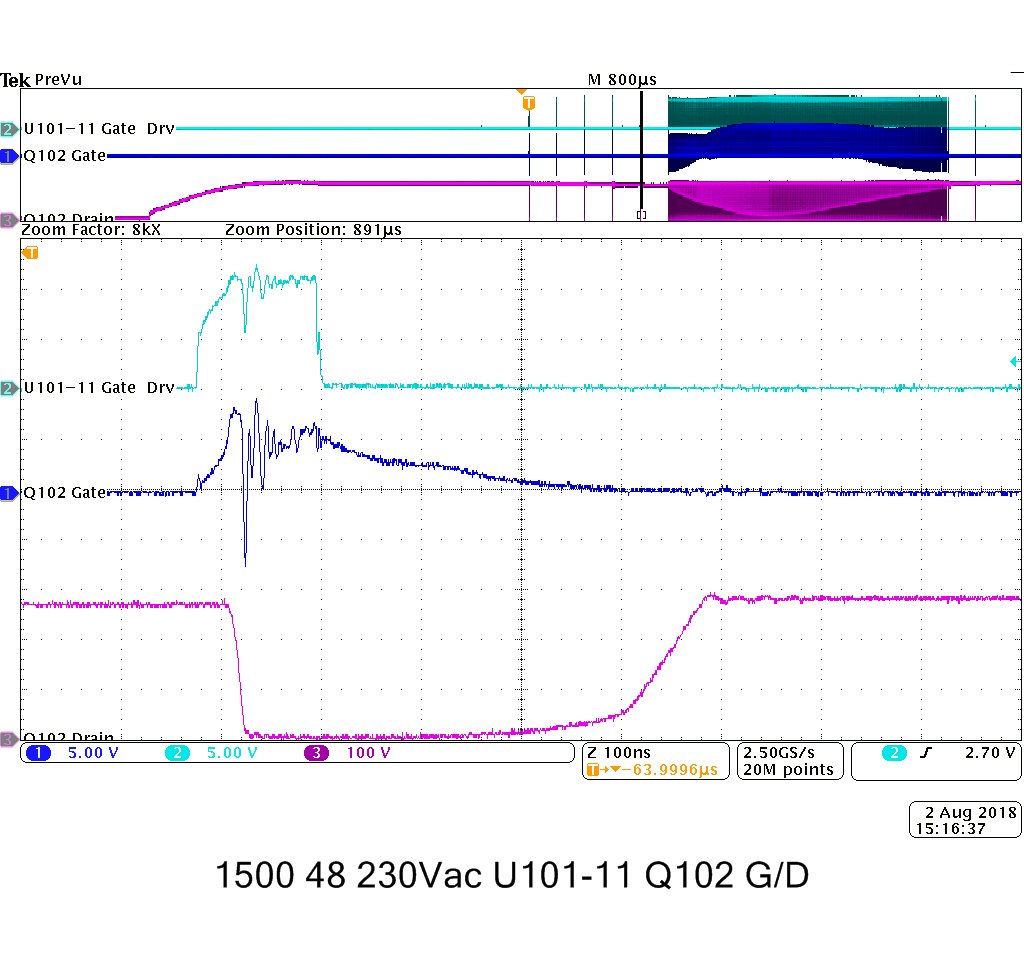

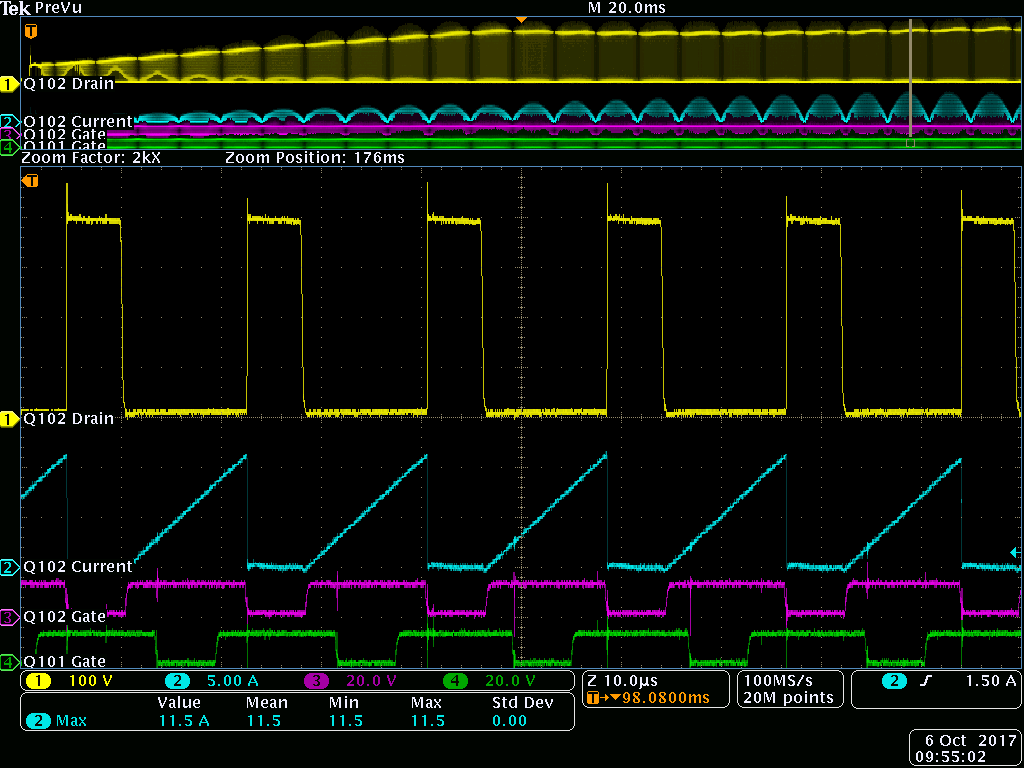

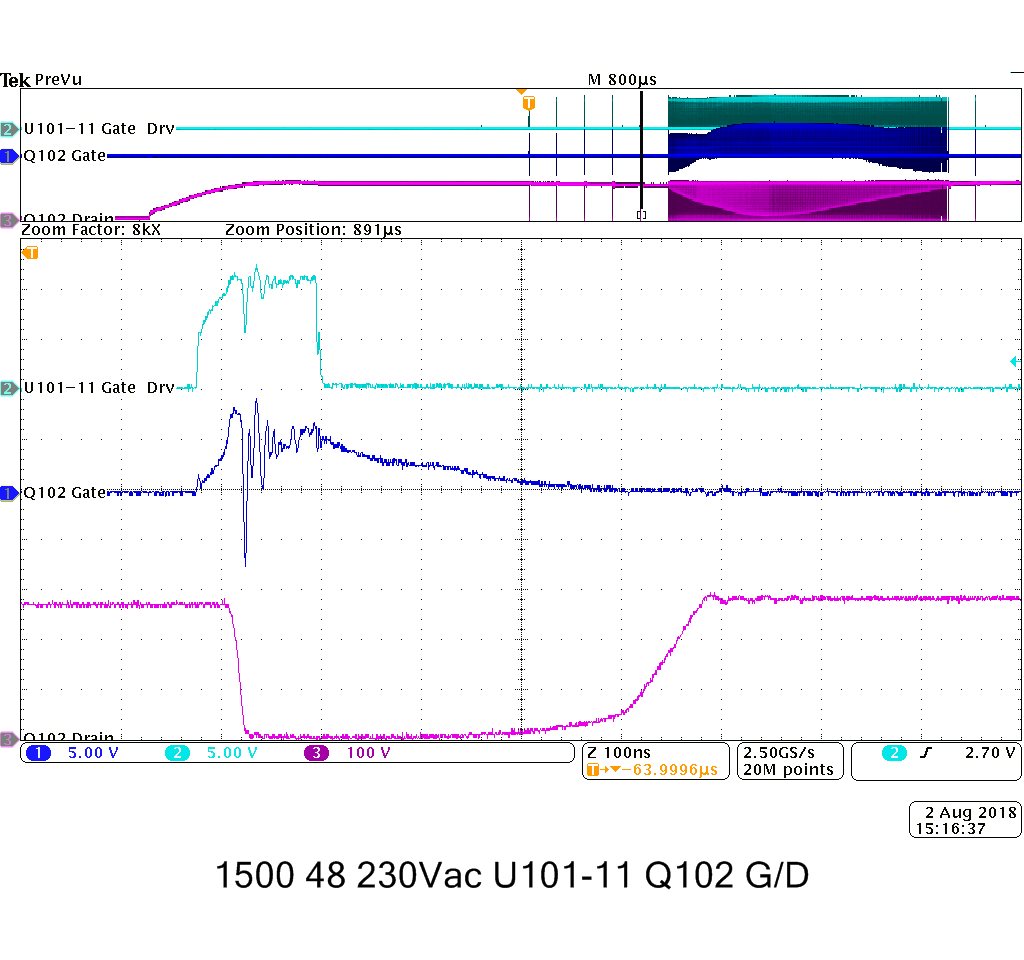

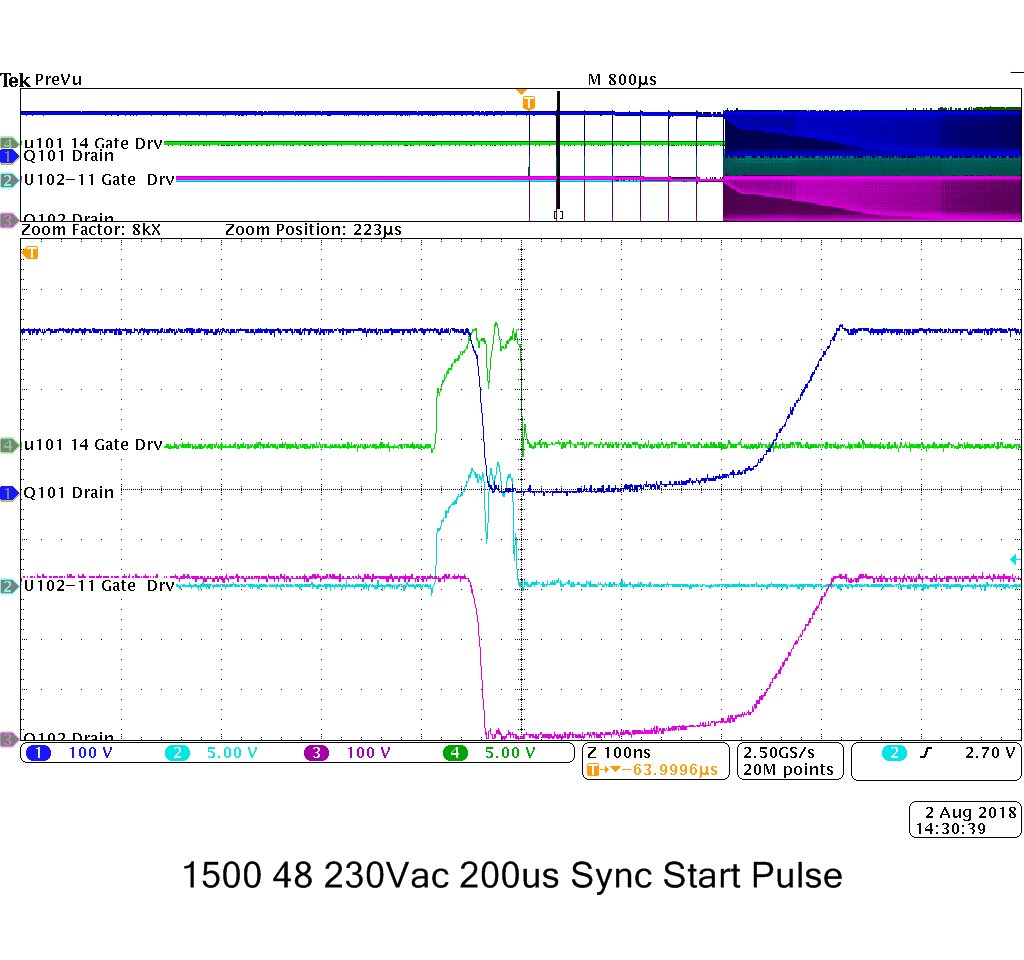

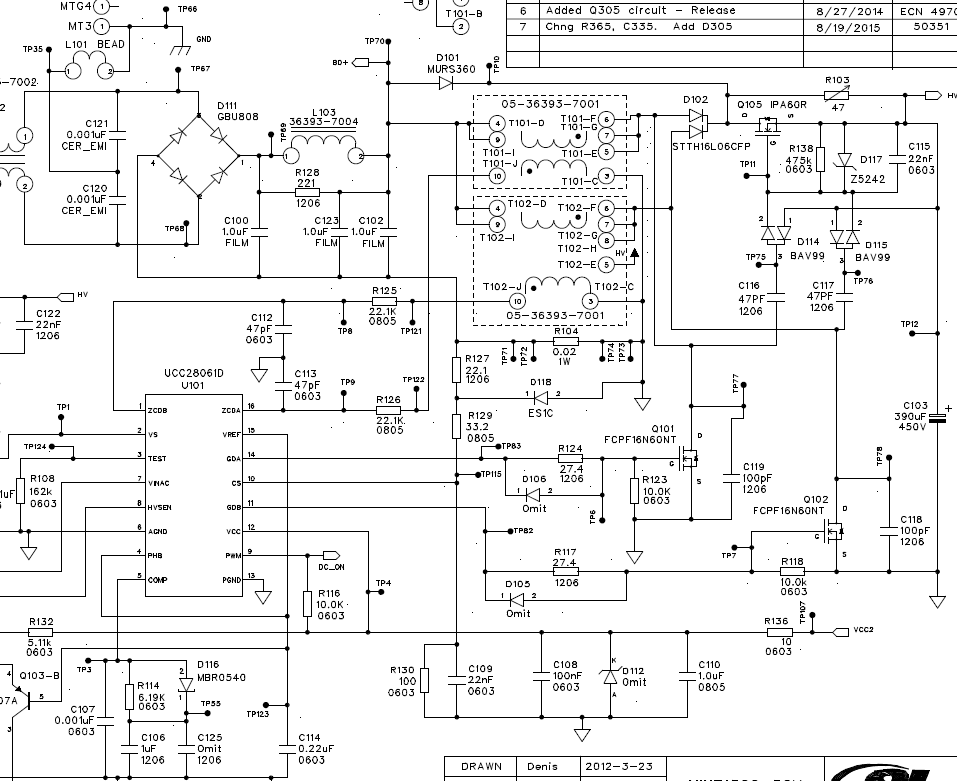

After updating from the older UCC28061 Interleaved PFC control IC to the newer "63A" version we have encountered failures of the "B" channel gate drive IC output. The boost converter simply stops running and the boost voltage drop to the peak line voltage of about 325 from a 230 Vac line input. After inspection of the IC we find an internal low resistances of from 2-50 ohms from GDB pin 11 to Vcc pin 12. Some failures may also develop low resistance of 2-200 ohms from the Gnd pin 3 to GDB pin 11. The GDA drive output shows no low resistance or signs of any stress. No other abnormalities appear on other pins of the IC or external components outside of the PFC converter control IC. The design has a 27.5 ohms series gate resistors on both the GDA and GDB gate drive outputs to the boost FET's. After the PFC control IC is replaced the power supply fuctions normally. The Controller is powered from a 13.4 VDC auxiliary power supply, runs at 70 kHz under full load and is capable of delivering 400VDC at 500W.

Is there any known history of gate driver "B" output failing in this manner ?

John