Hello dear Ti community.

I'm using your LDO's for more than few years.

My first choices are TPS7A4701/3301 and TPS7A49/30 and TPS7A39 (dual reg in one package).

I found some articles about improving LDO performance in many regions, including noise, PSRR etc.

Those articles are listed below :

My questions are :

- may I use it those reduction network for regulators listed above? (positive and negative), I read this article and I think it should be possible for all IC mentioned above.

- if I can adapt those network then how to calculate that RC value to obtain to achieve good compromise? Which parameters of LDO should I take to calculate everything myself?

- how about drawbacks (excluding start up time mentioned in arcticle and ofc cost and solution size), is there anything else that I should care about?

My design is very similiar to reference and it's follow design note.

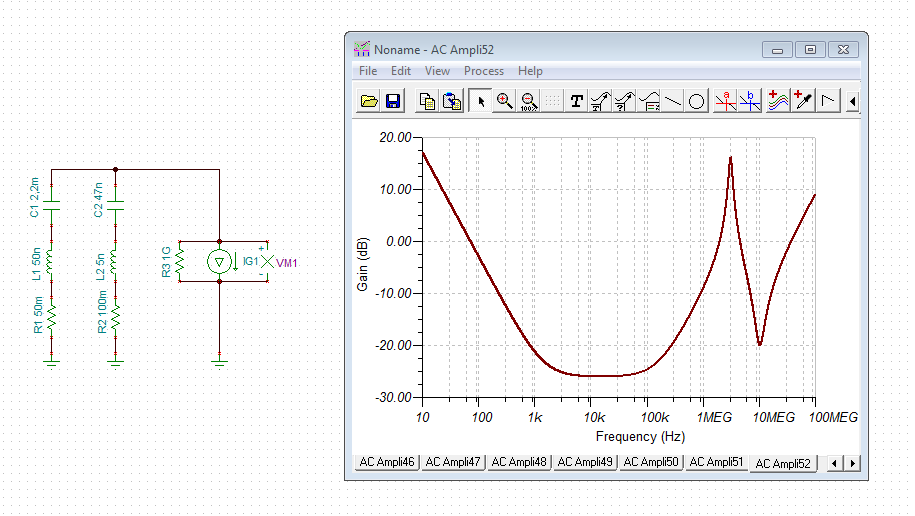

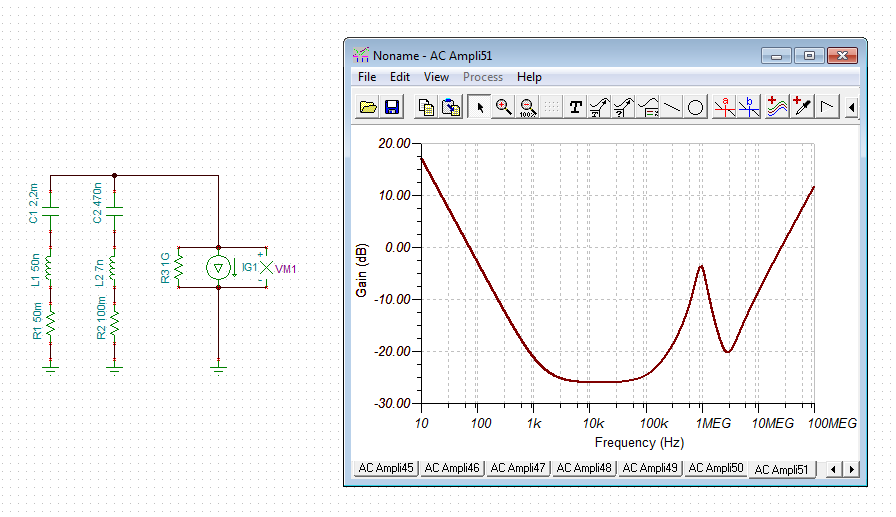

According to second article I've got questions about improving PSRR at LDO input.

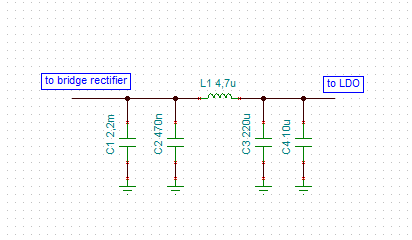

My PSU look like this :

IEC Inlet filter -> Toroidal transformer (hi quality) -> CRC snubber to damp trafo resonance -> bridge rectifier followed then by CRC filter (two big reservoir capacitors connected via small value resistor) -> LDO -> load.

Is there any chance to improve this design in terms of PSRR or overall performance?

I'm using those LDO's for audio application which include powering up DAC IC (or digital IC like SPDIF IC, DE/MUX etc.) or opamps (including hi current types like OPA1622 or LME49600).

So i want to achieve best possible performance with those applications.

According to Maxim desing note it would be best to place another LDO as a preregulator - but that solution will take some space and generate visible cost.

Maybe there will be some other ways to consider?

Thank you for helping me and your time.