Other Parts Discussed in Thread: TPS61230, TPS61230A

Hello everybody,

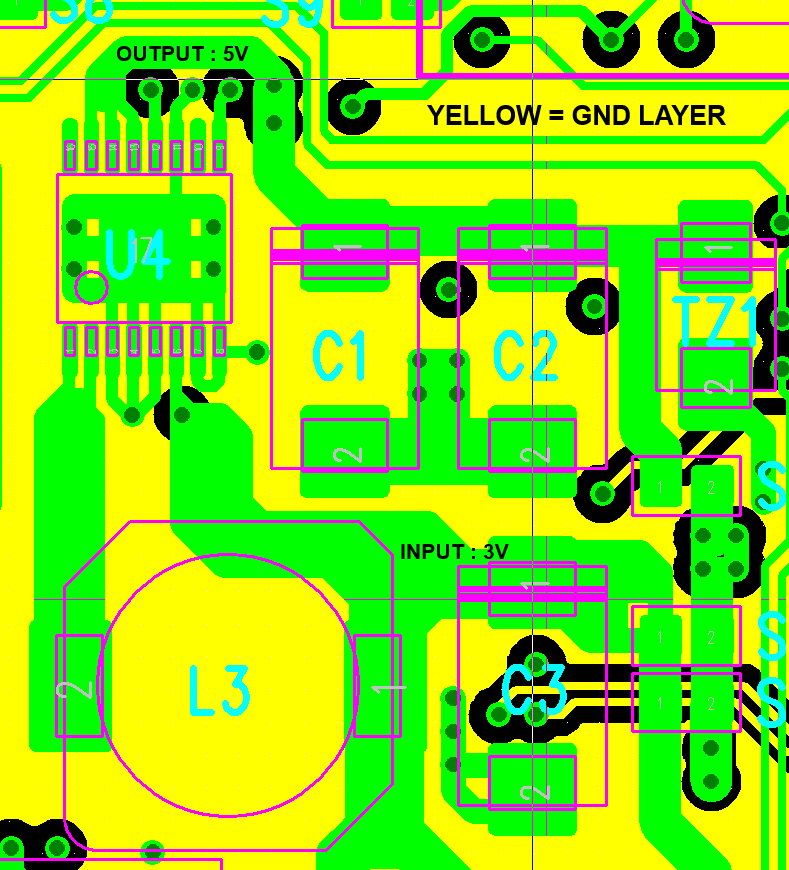

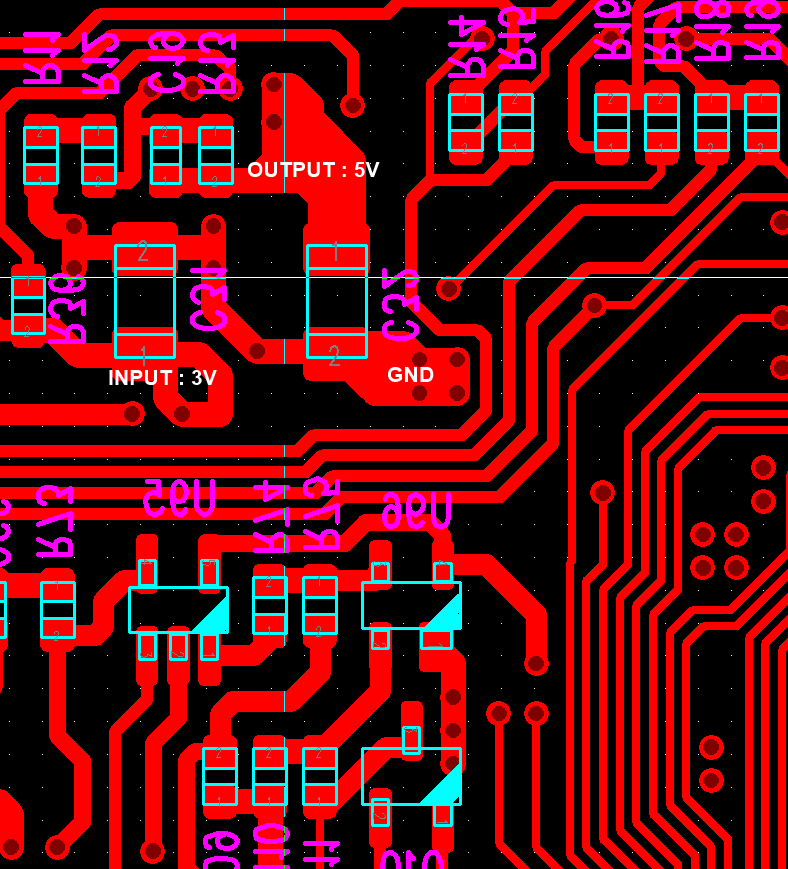

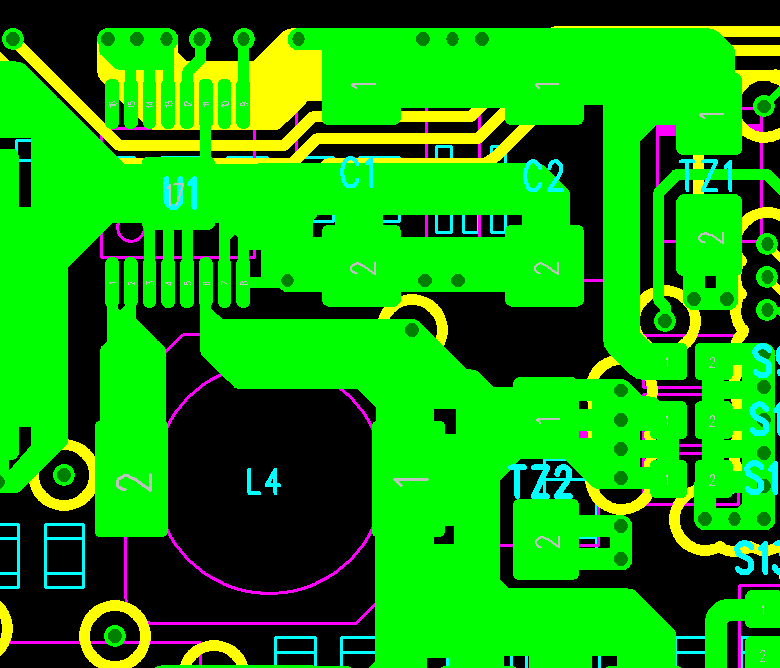

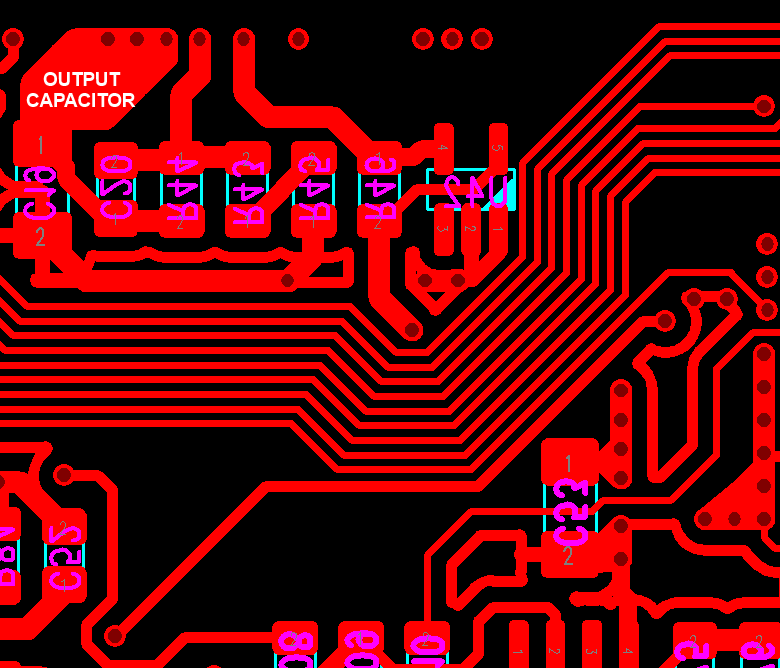

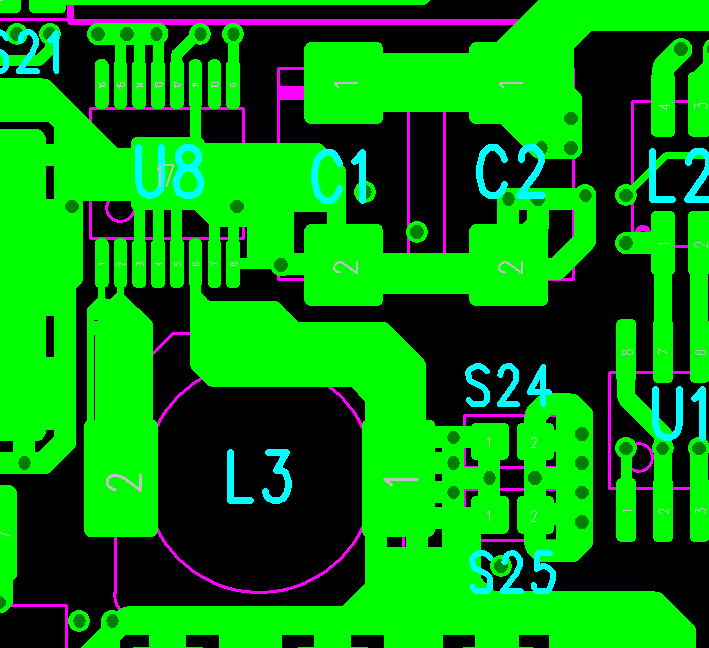

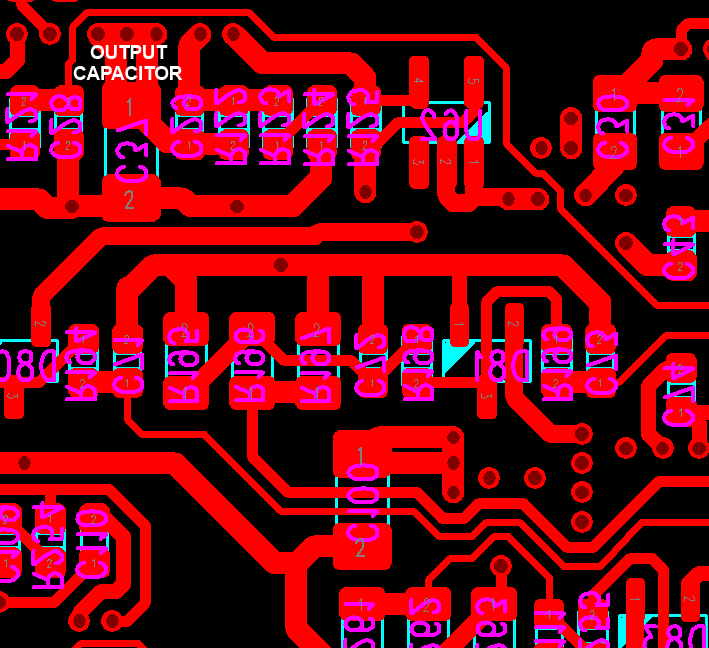

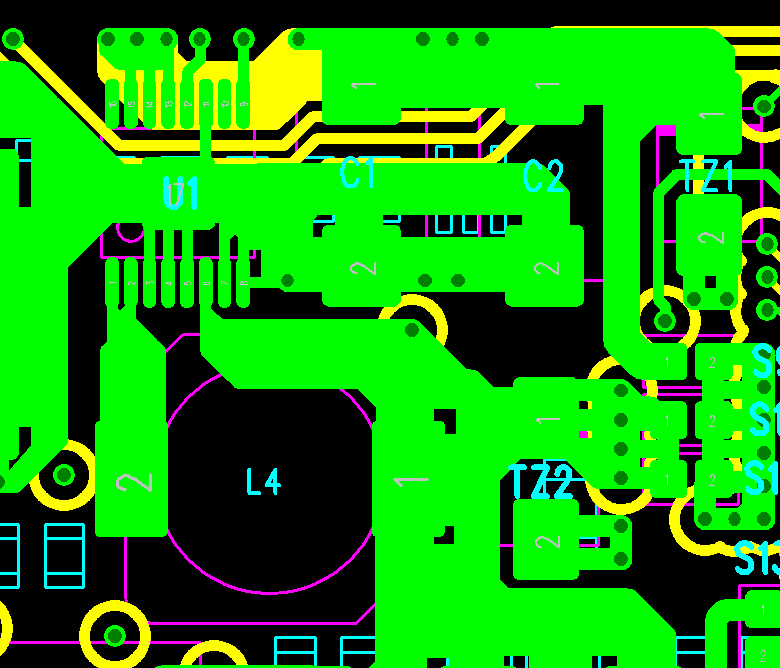

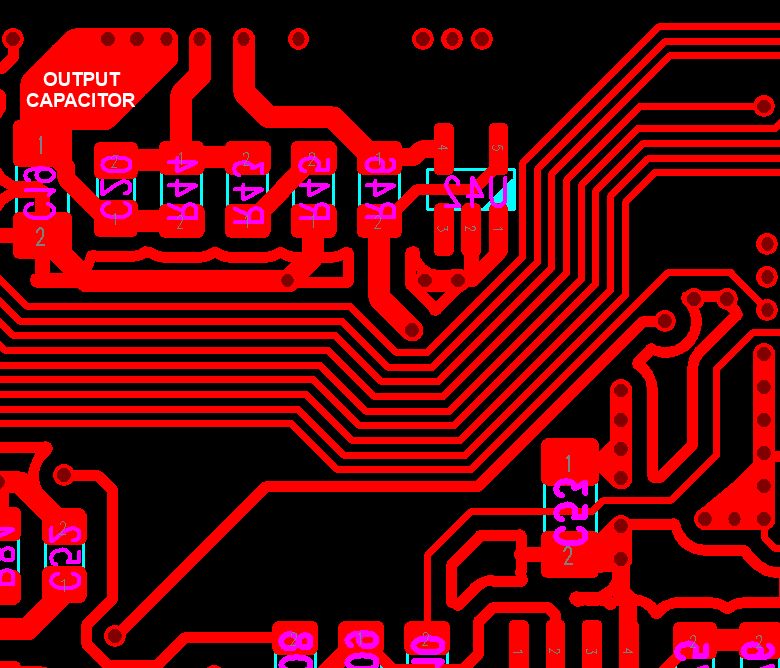

We are using a TPS61030, as a power supply for our product (a calculator for off road vehicles). You can see our schematics attached to this post.

We are experiencing some issues with this product. We already have two problematic cases. In those two cases the TPS61030 is returned broken from our client (approximately after 1 year of service). The component is in short circuit state.

We already have check our calculation for passive component selection (inductor, capacitor, feedback resistor) and the power rating of the TPS61030 compared to our need. For your information we have done the calculation for 1A output current (5V) and the measured current consumption is less than 250mA.

So we would like to have some help to find the root of this problem.

RegardsPower supply UC402.pdf