Hi TI Support Team

I want to double check with you about the TDA4 serdes physical layers interface.

Because PCIe / USB / SGMII / DP share same serdes in TDA4.

when we use SGMII from Serdes,

1. Do you know if it is CML I/O for TDA4 SGMII interface ? Which buffer in Serdes LVDS or CML or others IO?

2. Do we need enable TDA4 RX internal termination from SW ? which register can change it.

3. Do we need enable pre-emphasis in default from SW? which register can change it.

Currently our design ad below:

TDA4 TX ( which buffer ???) ====AC(100nF/0402)=======>PHY (CML I/O input / internal 100ohm input impedance)

TDA4 RX ( which buffer ???) <====AC(100nF/0402)=======PHY (CML I/O output)

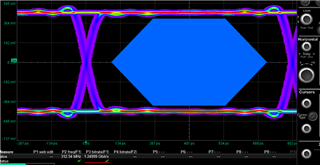

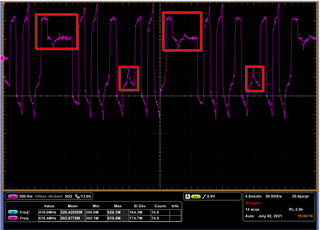

Some confuse about the TDA4 TX test waveform.

1. The level high and low in highlight area don't same as others level.

2. Does is cause by pre-emphasis from TDA4?

3. Does it is correct waveform ? Do you have your EVM test waveform for SGMII interfac. We can compare with us.

Thanks

Yutai