Other Parts Discussed in Thread: DRA829

We are verifying our LPDDR4 interface using Micron MT53D1024M32D4DT-046 at 3733-Mbps speed grade and see some issues with the quality of our data writes.

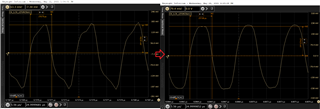

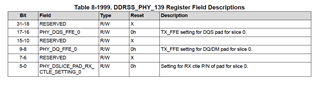

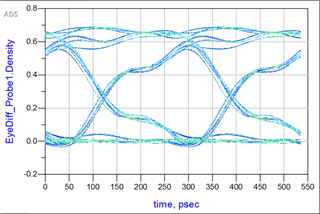

Data WRITE eye. DRA829 driving, measured at Micron chip.

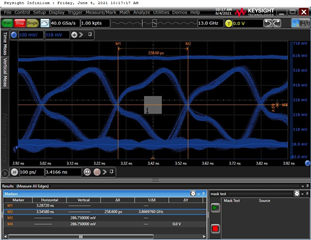

Meanwhile. our Data READ eye looks much better. (Micron chip transmitting, measured at DRA829).

The above images are shown using standard 40-ohm termination settings.

I have tried adjusting these values to dozens of different combinations. None of them seem to have more than a marginal effect on the signal integrity. The same general shape persists.

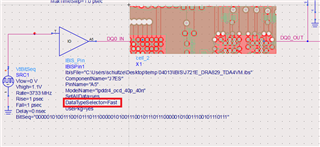

I was able to get an ADS simulation to show similar results, but only by changing the DataTypeSelector to "FAST", which also looks like it had some effect on the package RLC values

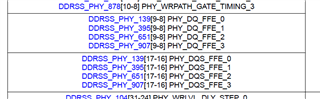

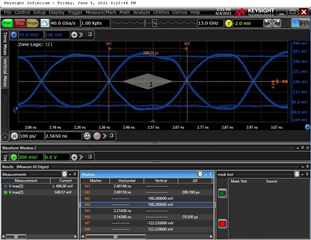

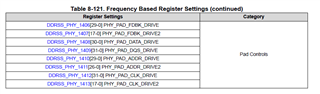

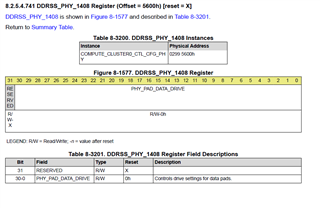

Reading through the TRM, I noticed this batch of registers which are referred to as Pad Controls.

However, the TRM isn't really helpful in the register description.

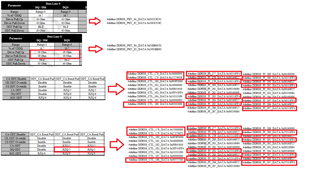

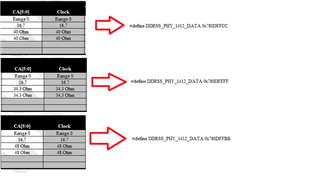

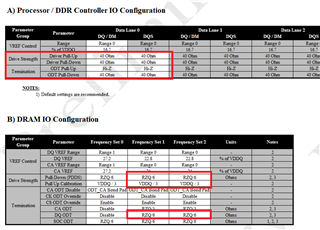

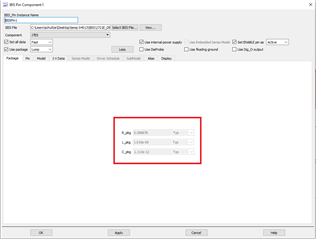

I do notice that when I adjust the termination settings in the J7 DDRSS Register Configuration spreadsheet, only the pad drive settings for the clock change with adjustments to the Address/Command termination configuration. Changing data/dqs termination does not appear to have any effect PHY_1408 register at all. Here is what we currently set the values to, based on the spreadsheet results.

I would like more information on what the registers are for, if they need to be adjusted from shown, a more detailed description of the bits etc. It's also possible I'm using an outdated version of the spreadsheet? It is dated August 4th, 2020 Rev 0.5.0. I attached it below.

I would check and compare it to our EVM board, but the vias are all backdrilled and there is no access to any of the DDR4 signals for probing. I am curious if/how TI managed to verify this interface on the EVM (interposer?).