Hello,

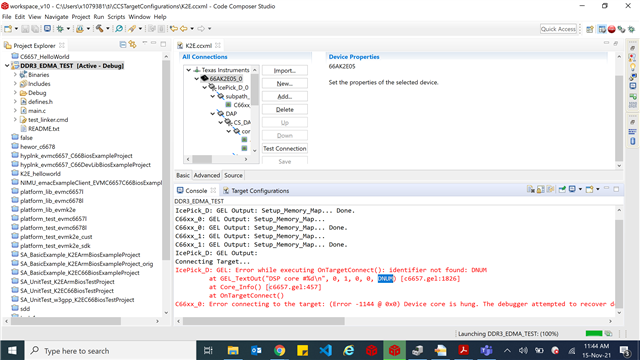

We observe RAM read errors on some of our products. The nature of the read errors is explained in the following attachments-Files :

KS2_DDR_Debug_Spreadsheet_v1_01_errata_applied_error_occurs.xlsx (Debug results after applying KeyStoneII.BTS_errata_advisory.35 in case of error)

KS2_DDR_Debug_Spreadsheet_v1_01_errata_applied_no_error.xlsx (Debug results after applying KeyStoneII.BTS_errata_advisory.35 in case of no error)

KS2_DDR_Debug_Spreadsheet_v1_01_without_errata_error_occurs.xlsx (Debug results befor applying KeyStoneII.BTS_errata_advisory.35 in case of error)

KS2_DDR_Debug_Spreadsheet_v1_01_without_errata_no_error.xlsx (Debug results befor applying KeyStoneII.BTS_errata_advisory.35 in case of no error)

we have noticed the KeyStoneII.BTS_errata_advisory.35 is not applied in our Products, but unfortunately applying KeyStoneII.BTS_errata_advisory.35 doesn't lose our problem.

we hope that you can help us to solve this problem

best regards

Muhand AlkhouriKS2_DDR_Debug_Spreadsheet_v1_01_errata_applied_error_occurs.xlsxKS2_DDR_Debug_Spreadsheet_v1_01_errata_applied_no_error.xlsxKS2_DDR_Debug_Spreadsheet_v1_01_without_errata_error_occurs.xlsxKS2_DDR_Debug_Spreadsheet_v1_01_without_errata_no_error.xlsx