Hello,

I am using a custom board based on the K2G Keystone. On of the changes is a NORFLASH connected through GPMC and I am trying to XIP from it.

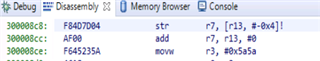

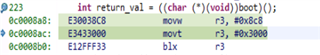

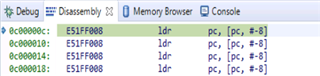

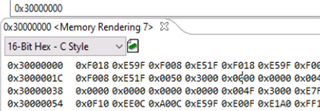

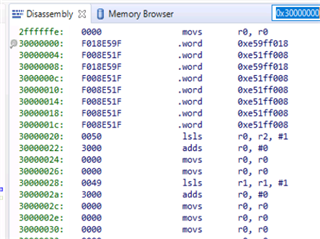

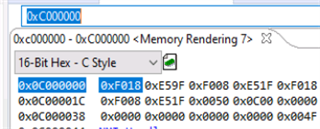

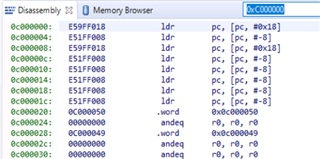

When using the debugger I can see binary data written into the NORFLASH (see 1st extract) but using the disassembly windows I am seeing no instructions recognized.

I am executing the same code out of the internal RAM (different start addr) and everything is fine with the code.

Can someone see what is going on here? I am very puzzled.

thank you,

Vincent