Hi team,

My customer encounters a very specific problem while using the 66AK2H14 on a custom board.

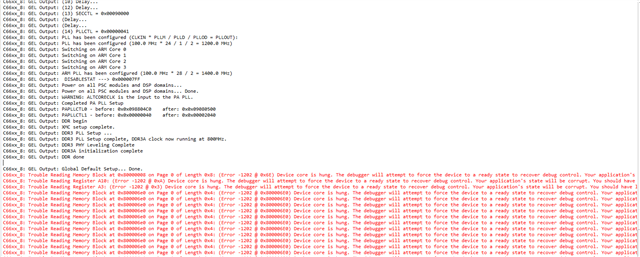

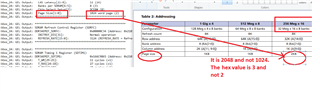

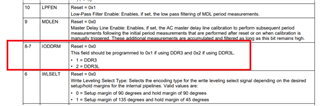

After connecting to the target, he runs the gel file, to initialize the SoC (very similar to the GEL by default on this version of CCSv910, ie log below). However, even if the DDR3 seems to be initialized properly, a DDR3 access (through memory browser or with a direct access through the ddr3A_memory_test () function for example) leads the CPU to crash.

- emulator is XDS560V2STM and CCSv910

- CCS sends the error -1202 ie below. This error is not specified here https://software-dl.ti.com/ccs/esd/documents/ccs_debugging_jtag_connectivity_issues.html#device-hung

- JTAG tests prove a correct physical interconnection with the DDR.

- The supply voltage of both the CPU and the DDR has been tested and don't show any problem.

-> How can a DDR access makes the CPU to crash ?

-> Do you have any explanation or recommendations on tests to be carried out ?

-> I saw a very similar post here https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1014972/66ak2g12-what-s-this-error-message-of-ccs-ddr-access-by-memory-browser/3751531?tisearch=e2e-sitesearch&keymatch=ERROR%201202#3751531 but has not been answered properly, have you found a solution since then?

Regards,

Geoffrey

Error connecting to the target: (Error -1202 @ 0x6E) Device core is hung. The debugger will attempt to forced the device to a ready state and recovered debug control, but your application's state will be corrupt. You should have limited access to memory and registers, but you may need to reset the device to debug further.