Hi there,

I'm working on a AM64x evaluation board TMDS64GPEVM, running FreeRTOS with mcu_plus_sdk_am64x_08_00_00_21.

This is a general question about .vectors section.

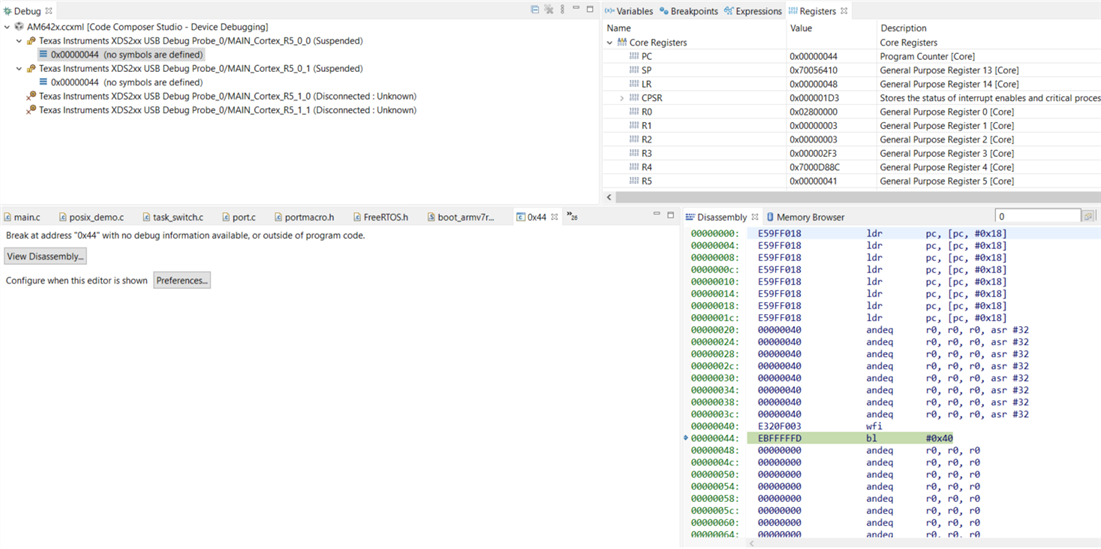

After powering up the board and connecting with XDS200 to R5_0_0 and R5_0_1 the memory at address 0x0 from the perspective of both core0 and core1 looks like this:

Using objdump on some .out file I can see the .vectors section:

Disassembly of section .vectors:

00000000 <_vectors>:

0: e59ff018 ldr pc, [pc, #24] ; 20 <reset_addr>

4: e59ff018 ldr pc, [pc, #24] ; 24 <undefined_addr>

8: e59ff018 ldr pc, [pc, #24] ; 28 <svc_addr>

c: e59ff018 ldr pc, [pc, #24] ; 2c <prefetch_abort_addr>

10: e59ff018 ldr pc, [pc, #24] ; 30 <data_abort_addr>

14: e59ff018 ldr pc, [pc, #24] ; 34 <reserved_addr>

18: e59ff018 ldr pc, [pc, #24] ; 38 <irq_addr>

1c: e59ff018 ldr pc, [pc, #24] ; 3c <fiq_addr>

00000020 <reset_addr>:

20: 70023fd4 ldrdvc r3, [r2], -r4

00000024 <undefined_addr>:

24: 70020727 andvc r0, r2, r7, lsr #14

00000028 <svc_addr>:

28: 70020b70 andvc r0, r2, r0, ror fp

0000002c <prefetch_abort_addr>:

2c: 70020745 andvc r0, r2, r5, asr #14

00000030 <data_abort_addr>:

30: 70020763 andvc r0, r2, r3, ror #14

00000034 <reserved_addr>:

34: 70020709 andvc r0, r2, r9, lsl #14

00000038 <irq_addr>:

38: 70020bf8 strdvc r0, [r2], -r8

0000003c <fiq_addr>:

3c: 70020651 andvc r0, r2, r1, asr r6

When connecting to core0 and loading an image I can see the vectors section properly loaded in address 0x0.

When connecting to core1 and examining the memory it looks like the image is properly loaded. I can see initialized variables and structures.

However, from core1 perspective the vector doesn't seem to be loaded.

How come it not visible from core1?

What is responsible for initializing this particular piece of memory? where is this code?

In the am64x TRM, Main domain memory map says that in address 0x0

PSRAMECC0_RAM 0x000000000 0x0000003FF 1 KB

Is this core specific area? not much is said about PSRAMECC0_RAM.

Please elaborate.

Thanks a lot,

Nir.