Hi,

I tried to debug mac to mac on SGMII port 5 & port 8.

I configured the SGMII mode to ENET_MAC_SGMIIMODE_SGMII_FORCEDLINK.

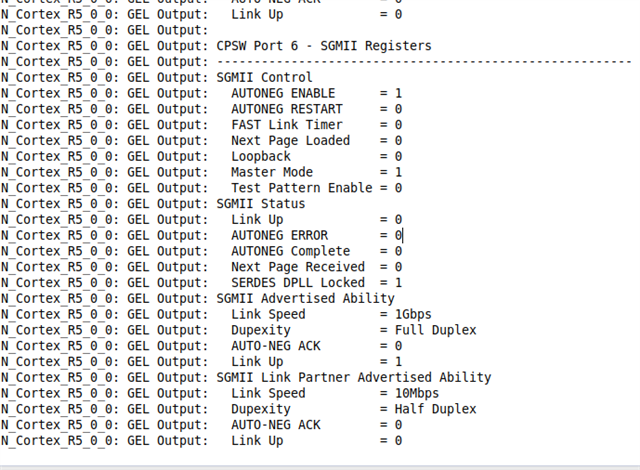

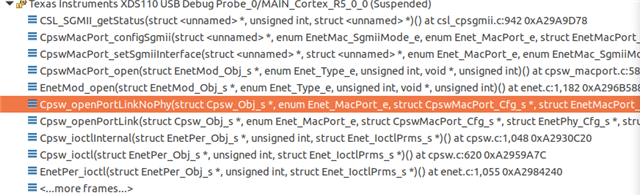

And I found SGMII port5 always stay at 'get SGMII status' as below:

There is no error information output in UART. And the value of register '0C000514h' is 0x00000030.

The SGMII port8 is the same as port5 and always stay at 'get SGMII status', but the value of register '0C000814h' is 0x0000003a.

I found the PLL of port8 sometime can't be locked, and sometimes can be locked.

Above all, the SGMII5 & 8 cann't link up. Do you have any suggestions to handle this issue? Thank you!

And for above if there is anything wrong, please tell us and I will try to debug it.

Best regards,

Lan