Hi TI,

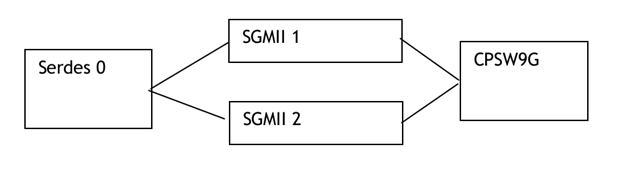

While developing the SGMII with SERDES0 on out custom board,we have met a problem that the serdes 0 can not be locked.

the RTOS SDK and linux kernel is version 8.0

the error is reported in

/* In case of SGMII, the MDIO controls the auto-negotiation of the PHY to the

* other side of the fiber or wire (ie. to the remote system). The CPSGMII is

* the link to the PHY. The PHY auto-negotiates with the other side and

* then the CPSGMII auto-negotiates with the PHY. */

/* Confirm SERDES PLL is locked before configuring the port */

if (CSL_SGMII_getSerdesPLLLockStatus(sgmiiRegs, portNum) == 0U)

{

ENETTRACE_ERR("MAC %u: SERDES PLL is not locked\n", portId);

status = ENET_EUNEXPECTED;

}the serial print shows the serdes is not locked: (I added some printf)

the modifications are:

static Board_STATUS Board_CfgSgmiiSerdes0(void)

{

CSL_SerdesResult result;

CSL_SerdesLaneEnableStatus laneRetVal = CSL_SERDES_LANE_ENABLE_NO_ERR;

CSL_SerdesLaneEnableParams serdesLane0EnableParams = {0};

memset(&serdesLane0EnableParams, 0, sizeof(serdesLane0EnableParams));

/* QSGMII Config */

serdesLane0EnableParams.serdesInstance = (CSL_SerdesInstance)CSL_SIERRA_SERDES0;

serdesLane0EnableParams.baseAddr = CSL_SERDES_16G0_BASE;

serdesLane0EnableParams.refClock = CSL_SERDES_REF_CLOCK_19p2M;

serdesLane0EnableParams.refClkSrc = CSL_SERDES_REF_CLOCK_INT;

serdesLane0EnableParams.linkRate = CSL_SERDES_LINK_RATE_1p25G;

serdesLane0EnableParams.numLanes = 0x2;

serdesLane0EnableParams.laneMask = 0x3;

serdesLane0EnableParams.SSC_mode = CSL_SERDES_NO_SSC;

// serdesLane0EnableParams.phyType = CSL_SERDES_PHY_TYPE_QSGMII;

serdesLane0EnableParams.phyType = CSL_SERDES_PHY_TYPE_SGMII;

serdesLane0EnableParams.operatingMode = CSL_SERDES_FUNCTIONAL_MODE;

serdesLane0EnableParams.phyInstanceNum = SERDES_LANE_SELECT_CPSW;

serdesLane0EnableParams.pcieGenType = CSL_SERDES_PCIE_GEN3;

serdesLane0EnableParams.laneCtrlRate[0] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[0] = CSL_SERDES_LOOPBACK_DISABLED;

serdesLane0EnableParams.laneCtrlRate[1] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[1] = CSL_SERDES_LOOPBACK_DISABLED;

CSL_serdesPorReset(serdesLane0EnableParams.baseAddr);

/* Select the IP type, IP instance num, Serdes Lane Number */

CSL_serdesIPSelect(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.phyType,

serdesLane0EnableParams.phyInstanceNum,

serdesLane0EnableParams.serdesInstance,

2);

result = CSL_serdesRefclkSel(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.baseAddr,

serdesLane0EnableParams.refClock,

serdesLane0EnableParams.refClkSrc,

serdesLane0EnableParams.serdesInstance,

serdesLane0EnableParams.phyType);

if (result != CSL_SERDES_NO_ERR)

{

return BOARD_FAIL;

}

CSL_FINSR(*(volatile uint32_t *)(uintptr_t)(0x05000408),29,28,0x1);

// add modified 3 line directly change register

CSL_FINSR(*(volatile uint32_t *)(uintptr_t)(0x05000408),31,30,0x0);

CSL_FINSR(*(volatile uint32_t *)(uintptr_t)(0x05000480),25,24,0x0);

CSL_FINSR(*(volatile uint32_t *)(uintptr_t)(0x05000488),5,0,0x0);

/* Assert PHY reset and disable all lanes */

CSL_serdesDisablePllAndLanes(serdesLane0EnableParams.baseAddr, serdesLane0EnableParams.numLanes, serdesLane0EnableParams.laneMask);

/* Load the Serdes Config File */

result = CSL_serdesEthernetInit(&serdesLane0EnableParams);

/* Return error if input params are invalid */

if (result != CSL_SERDES_NO_ERR)

{

return BOARD_FAIL;

}

/* Common Lane Enable API for lane enable, pll enable etc */

laneRetVal = CSL_serdesLaneEnable(&serdesLane0EnableParams);

if (laneRetVal != 0)

{

return BOARD_FAIL;

}

return BOARD_SOK;

}

@@ -572,8 +600,7 @@

};

&serdes_ln_ctrl {

- idle-states = <J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_IP4_UNUSED>,

- <J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

+ idle-states = <J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANE0_IP1_UNUSED>, <J721E_SERDES2_LANE1_USB3_1>,

<J721E_SERDES3_LANE0_USB3_0_SWAP>, <J721E_SERDES3_LANE1_USB3_0>,

<J721E_SERDES4_LANE0_EDP_LANE0>, <J721E_SERDES4_LANE1_EDP_LANE1>,

@@ -689,16 +716,26 @@

&mcu_cpsw {

pinctrl-names = "default";

- pinctrl-0 = <&mcu_cpsw_pins_default &mcu_mdio_pins_default>;

+ pinctrl-0 = <&mcu_cpsw_pins_default &mcu_mdio_pins_default &phy_reset_pins_default>;

};

@@ -50,7 +50,6 @@

/* mux-reg-masks = <0x4080 0x3>, <0x4084 0x3>,*/ /* SERDES0 lane0/1 select */

/*<0x4090 0x3>, <0x4094 0x3>, */ /* SERDES1 lane0/1 select */

mux-reg-masks =

- <0x4080 0x3>, <0x4084 0x3>, /* SERDES0 lane0/1 select */

<0x4090 0x3>, <0x4094 0x3>, /* SERDES1 lane0/1 select */

<0x40a0 0x3>, <0x40a4 0x3>, /* SERDES2 lane0/1 select */

<0x40b0 0x3>, <0x40b4 0x3>, /* SERDES3 lane0/1 select */

@@ -58,8 +57,7 @@

/* SERDES4 lane0/1/2/3 select */

/* idle-states = <J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_PCIE0_LANE1>,

<J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>, */

- idle-states = <J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_PCIE0_LANE1>,

- <J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

+ idle-states = <J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANE0_IP1_UNUSED>, <J721E_SERDES2_LANE1_USB3_1>,

<MUX_IDLE_AS_IS>, <J721E_SERDES3_LANE1_USB3_0>,

<J721E_SERDES4_LANE0_EDP_LANE0>, <J721E_SERDES4_LANE1_EDP_LANE1>,

@@ -598,6 +596,7 @@

};

pcie0_rc: pcie@2900000 {

+ status="disabled";

compatible = "ti,j721e-pcie-host";

reg = <0x00 0x02900000 0x00 0x1000>,

<0x00 0x02907000 0x00 0x400>,

@@ -639,6 +638,7 @@

};

pcie0_ep: pcie-ep@2900000 {

+ status="disabled";

compatible = "ti,j721e-pcie-ep";

reg = <0x00 0x02900000 0x00 0x1000>,

<0x00 0x02907000 0x00 0x400>,

Please help to config the serdes 0 to be locked ,thanks a lot.