Other Parts Discussed in Thread: SYSCONFIG

Hi Team AM4,

My Customer has the following questions..

Our team needs clarification regarding the use of SPI0 NOR Flash. Appreciate your response on this.

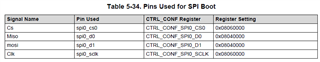

Presently we are using SPI0 NOR Flash for booting the board. We are also in need of using PRU ICSSS 0 UART for our serial communication in addition to the other existing UARTS. But this is creating conflicts with the pins where we are looking for swapping SPI0 NOR Flash to some other pins. Here, instead of utilizing default SPI0 pins for NOR Flash where MLO is stored for booting the device, we want to use alternative SPI0 pins (SPI0_CS0; AD25, SPI0_d1; AB25, SPI0_SCLK; AE21) for interfacing the SPI NOR Flash. We want to understand if the Boot ROM can detect the SPI NOR flash if we move the SPI NOR flash to alternative SPI0 pins.

Since we have SPI0 default pins conflicting with PRU ICSS 0, we are also evaluating alternative approach to drop the SPI NOR flash and load MLO in eMMC boot0/boot1 partition. This is not the first FAT partition of the eMMC (FAT32). This is the boot area provided by the eMMC vendor to store the bootloader/boot config data. We want to understand whether the present TI uBoot is supporting boot0/boot1 partitions along with secure boot implementation.

Also, we observed that it takes around 10 to 15 seconds to load the MLO from SPI0 NOR Flash. Is there a way to optimize this?

Our team need a clarification regarding the use of SPI0 NOR Flash. Appreciate your response on this.

Thanks, Merril