We have configured connected ADV7391 on VOUT2 port of AM5728. We want to display CVBS video on LCD.

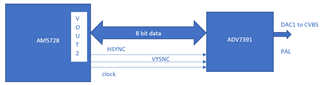

Following is the HW pipeline

AM5728 DSS VOUT2(BT656) -> ADV7391(video encoder) -> LCD(CVBS)

We have followed below mentioned document to bypass video pipeline as mentioned in section 2.3.2

https://www.ti.com/lit/an/sprac16a/sprac16a.pdf

we had tried to modify in existing software driver to configure DSS BT656 for 8 bit interface.

Following is the device tree changes:

&dss {

ports {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

port@1 {

reg = <1>;

dpi_out2: endpoint {

data-lines = <16>;

remote-endpoint = <&adv7391_in>;

};

};

port@2 {

reg = <2>;

dpi_out: endpoint {

data-lines = <24>;

remote-endpoint = <&lcd_in>;

};

};

};

};

sample-panel.c changes:

static const struct panel_desc pdic_display_adv7391 = {

.modes = &pdic_display_adv7391_mode,

.num_modes = 1,

.bpc = 8,

.size = {

.width = 130,

.height = 98,

},

.bus_format = MEDIA_BUS_FMT_RGB565_1X16,

};

The changes of DSS driver Attached

Request your help in below points on software side:

-

Is it possible to run BT.656 mode with external sync?

-

What should be AM5728 configuration for DSS to output YUV422 8-bit (BT.656) with embedded sync and/or external sync?