Hi, TI support team.

PSDKRA8.1 & PSDKLA8.1 & Custom Board, PSDKLA8.1 don not soupport DSI driver. So we choose to use DSI interface to show iamge(1920x1080) obtained from camera(s) in RTOS.

1. Current goal is to achieve one screen that can be displayed.

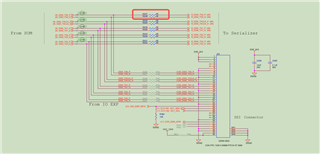

2. Ultimate goal is to use TAD4 output superframe to Serializer, and then the serializer is responsible for dividing the image(2*1920 x 1080) into two identical sizes(1920 x 1080) for two display panels.

The 1-step failed. ./run_app_single_cam.sh

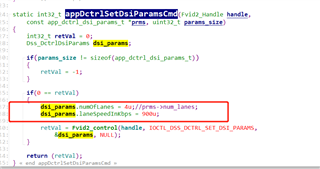

Below show my modifications in files:

diff --git a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/pdk_jacinto_08_01_00_36/packages/ti/drv/dss/include/dss_dctrl.h b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/pdk_jacinto_08_01_00_36/packages/ti/drv/dss/include/dss_dctrl.h

index cafefd617..ad8bdd6e3 100755

--- a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/pdk_jacinto_08_01_00_36/packages/ti/drv/dss/include/dss_dctrl.h

+++ b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/pdk_jacinto_08_01_00_36/packages/ti/drv/dss/include/dss_dctrl.h

@@ -604,6 +604,12 @@ typedef struct

/**< DSI Instance ID, currently note used */

uint32_t numOfLanes;

/**< Number of outputs lanes for DSI output, max 4 */

+ uint32_t laneSpeedInKbps;

+ /**< Exact DPHY lane speed from the selected speed band in Megabits per sec.

+ * This parameter is set to default value during init time.

+ * If updated in the application after init, newly set value will be used

+ * for DPHY clock configurations.

+ */

} Dss_DctrlDsiParams;

/* ========================================================================== */

diff --git a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/pdk_jacinto_08_01_00_36/packages/ti/drv/dss/src/drv/dctrl/dss_dctrlDsi.c b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/pdk_jacinto_08_01_00_36/packages/ti/drv/dss/src/drv/dctrl/dss_dctrlDsi.c

index 162ee9420..d8c544f05 100755

--- a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/pdk_jacinto_08_01_00_36/packages/ti/drv/dss/src/drv/dctrl/dss_dctrlDsi.c

+++ b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/pdk_jacinto_08_01_00_36/packages/ti/drv/dss/src/drv/dctrl/dss_dctrlDsi.c

@@ -69,6 +69,7 @@

#define DPHYTX0_CORE_BASE (CSL_DPHY_TX0_BASE)

/* Base Address of DSI Wrapper */

#define DSITX2_WRAP_REGS_BASE (CSL_DSS_DSI0_DSI_WRAP_MMR_VBUSP_CFG_DSI_WRAP_BASE)

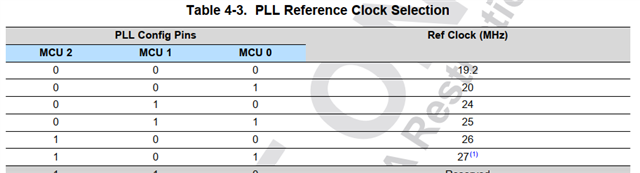

+#define DSITX_DPHY_REF_CLK_KHZ_DEF (19200U)

/* ========================================================================== */

@@ -100,6 +101,22 @@ typedef struct

} Dss_DctrlDSIDrvObj;

+/**

+ * struct Dsitx_DphyRangeData

+ *

+ * \brief This structure holds information about DSI Tx Range. Typically used

+ * for DPHY programming.

+ *

+ */

+typedef struct

+{

+ uint32_t rangeMin;

+ /**< Lower boundary of the range */

+ uint32_t rangeMax;

+ /**< Hogher boundary of the range */

+ uint32_t progVal;

+ /**< Value to be programmed for given range */

+} Dsitx_DphyRangeData;

/* ========================================================================== */

@@ -128,6 +145,185 @@ extern "C" {

static Dss_DctrlDSIDrvObj gDssDctrlDsiDrvObj;

+/* This contains information of the PLL input divider value for DPHY

+ rangeMin and rangeMax is in KHz */

+

+static Dsitx_DphyRangeData gDsiTxIpDivInfo[] =

+{

+ {

+ .rangeMin = 9600U,

+ .rangeMax = 19200U,

+ .progVal = 1U,

+ },

+ {

+ .rangeMin = 19200U,

+ .rangeMax = 38400U,

+ .progVal = 2U,

+ },

+ {

+ .rangeMin = 38400U,

+ .rangeMax = 76800U,

+ .progVal = 4U,

+ },

+ {

+ .rangeMin = 76800U,

+ .rangeMax = 150000U,

+ .progVal = 8U,

+ },

+};

+

+/* This contains information of the PLL output divider value for DPHY

+ rangeMin and rangeMax is in Mbps */

+static Dsitx_DphyRangeData gDsiTxOpDivInfo[] =

+{

+ {

+ .rangeMin = 1250U,

+ .rangeMax = 2500U,

+ .progVal = 1U,

+ },

+ {

+ .rangeMin = 630U,

+ .rangeMax = 1240U,

+ .progVal = 2U,

+ },

+ {

+ .rangeMin = 320U,

+ .rangeMax = 620U,

+ .progVal = 4U,

+ },

+ {

+ .rangeMin = 160U,

+ .rangeMax = 310U,

+ .progVal = 8U,

+ },

+ {

+ .rangeMin = 80U,

+ .rangeMax = 150U,

+ .progVal = 16U,

+ },

+};

+

+/* This contains information of the PLL output divider value for DPHY

+ rangeMin and rangeMax is in Mbps */

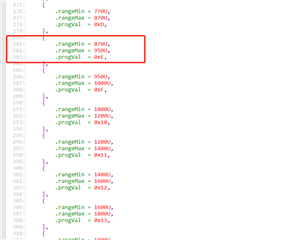

+static Dsitx_DphyRangeData gDsiTxLaneSpeedBandInfo[] =

+{

+ {

+ .rangeMin = 80U,

+ .rangeMax = 100U,

+ .progVal = 0x0,

+ },

+ {

+ .rangeMin = 100U,

+ .rangeMax = 120U,

+ .progVal = 0x1,

+ },

+ {

+ .rangeMin = 120U,

+ .rangeMax = 160U,

+ .progVal = 0x2,

+ },

+ {

+ .rangeMin = 160U,

+ .rangeMax = 200U,

+ .progVal = 0x3,

+ },

+ {

+ .rangeMin = 200U,

+ .rangeMax = 240U,

+ .progVal = 0x4,

+ },

+ {

+ .rangeMin = 240U,

+ .rangeMax = 320U,

+ .progVal = 0x5,

+ },

+ {

+ .rangeMin = 320U,

+ .rangeMax = 390U,

+ .progVal = 0x6,

+ },

+ {

+ .rangeMin = 390U,

+ .rangeMax = 450U,

+ .progVal = 0x7,

+ },

+ {

+ .rangeMin = 450U,

+ .rangeMax = 510U,

+ .progVal = 0x8,

+ },

+ {

+ .rangeMin = 510U,

+ .rangeMax = 560U,

+ .progVal = 0x9,

+ },

+ {

+ .rangeMin = 560U,

+ .rangeMax = 640U,

+ .progVal = 0xA,

+ },

+ {

+ .rangeMin = 640U,

+ .rangeMax = 690U,

+ .progVal = 0xB,

+ },

+ {

+ .rangeMin = 690U,

+ .rangeMax = 770U,

+ .progVal = 0xC,

+ },

+ {

+ .rangeMin = 770U,

+ .rangeMax = 870U,

+ .progVal = 0xD,

+ },

+ {

+ .rangeMin = 870U,

+ .rangeMax = 950U,

+ .progVal = 0xE,

+ },

+ {

+ .rangeMin = 950U,

+ .rangeMax = 1000U,

+ .progVal = 0xF,

+ },

+ {

+ .rangeMin = 1000U,

+ .rangeMax = 1200U,

+ .progVal = 0x10,

+ },

+ {

+ .rangeMin = 1200U,

+ .rangeMax = 1400U,

+ .progVal = 0x11,

+ },

+ {

+ .rangeMin = 1400U,

+ .rangeMax = 1600U,

+ .progVal = 0x12,

+ },

+ {

+ .rangeMin = 1600U,

+ .rangeMax = 1800U,

+ .progVal = 0x13,

+ },

+ {

+ .rangeMin = 1800U,

+ .rangeMax = 2000U,

+ .progVal = 0x14,

+ },

+ {

+ .rangeMin = 2000U,

+ .rangeMax = 2200U,

+ .progVal = 0x15,

+ },

+ {

+ .rangeMin = 2200U,

+ .rangeMax = 2500U,

+ .progVal = 0x16,

+ },

+};

+

/* ========================================================================== */

/* Internal/Private Function Declarations */

@@ -156,6 +352,7 @@ static int32_t dssDctrlEnableDsiLink(Dss_DctrlDSIDrvObj *dsiObj);

static int32_t dssDctrlEnableDsiDatapath(Dss_DctrlDSIDrvObj *dsiObj);

static int32_t dssDctrlWaitForLaneReady(Dss_DctrlDSIDrvObj *dsiObj);

+static int32_t dssdctrlCalcDsiParams(Dss_DctrlDSIDrvObj *dsiObj, const Dss_DctrlDsiParams *dsiPrms);

/* ========================================================================== */

/* Function Definitions */

@@ -183,8 +380,8 @@ void Dss_dctrlDrvInitDSI()

dsiObj->dphyTxOpDiv = 0x2;

dsiObj->dphyTxFbDiv = 0x173;

dsiObj->dphyTxRate = 0x1CE;

- dsiObj->cfgDsiTx.numOfLanes = 0x2u;

- dsiObj->privDsiTx.numOfLanes = 0x2u;

+ dsiObj->cfgDsiTx.numOfLanes = 0x4u;//0x2u;

+ dsiObj->privDsiTx.numOfLanes = 0x4u;//0x2u;

}

int32_t Dss_dctrlDrvSetDSIParams(Dss_DctrlDrvInfo *drvInfo,

@@ -198,6 +395,8 @@ int32_t Dss_dctrlDrvSetDSIParams(Dss_DctrlDrvInfo *drvInfo,

dsiObj->cfgDsiTx.numOfLanes = dsiPrms->numOfLanes;

dsiObj->privDsiTx.numOfLanes = dsiPrms->numOfLanes;

+ status = dssdctrlCalcDsiParams(dsiObj, dsiPrms);

+

/* Checks to see if the configuration (num of lanes) is valid */

status = DSITX_Probe(&dsiObj->cfgDsiTx, &dsiObj->sysReqDsiTx);

if (CDN_EOK == status)

@@ -294,6 +493,105 @@ int32_t Dss_dctrlDrvEnableVideoDSI(Dss_DctrlDrvInfo *drvInfo,

/* Internal/Private Function Definitions */

/* ========================================================================== */

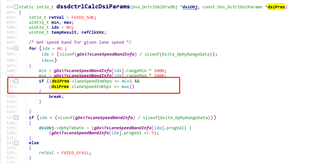

+static int32_t dssdctrlCalcDsiParams(Dss_DctrlDSIDrvObj *dsiObj, const Dss_DctrlDsiParams *dsiPrms)

+{

+ int32_t retVal = FVID2_SOK;

+ uint32_t min, max;

+ uint32_t idx = 0U;

+ uint64_t tempResult, refClkKHz;

+

+ /* Get speed band for given lane speed */

+ for (idx = 0U ;

+ idx < (sizeof(gDsiTxLaneSpeedBandInfo) / sizeof(Dsitx_DphyRangeData));

+ idx++)

+ {

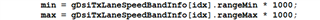

+ min = gDsiTxLaneSpeedBandInfo[idx].rangeMin * 1000;

+ max = gDsiTxLaneSpeedBandInfo[idx].rangeMax * 1000;

+ if ((dsiPrms->laneSpeedInKbps >= min) &&

+ (dsiPrms->laneSpeedInKbps <= max))

+ {

+ break;

+ }

+

+ }

+ if (idx < (sizeof(gDsiTxLaneSpeedBandInfo) / sizeof(Dsitx_DphyRangeData)))

+ {

+ dsiObj->dphyTxRate = (gDsiTxLaneSpeedBandInfo[idx].progVal) |

+ (gDsiTxLaneSpeedBandInfo[idx].progVal << 5);

+ }

+ else

+ {

+ retVal = FVID2_EFAIL;

+ }

+

+ if (retVal == FVID2_SOK)

+ {

+ /* TODO: Read the clock runtime through sciclient APIs */

+ refClkKHz = DSITX_DPHY_REF_CLK_KHZ_DEF;

+ /* Calculate DPHY ipdiv - PLL input divider */

+ if (retVal == FVID2_SOK)

+ {

+ for (idx = 0U ;

+ idx < (sizeof(gDsiTxIpDivInfo) / sizeof(Dsitx_DphyRangeData));

+ idx++)

+ {

+ if ((refClkKHz >= gDsiTxIpDivInfo[idx].rangeMin) &&

+ (refClkKHz < gDsiTxIpDivInfo[idx].rangeMax))

+ {

+ break;

+ }

+ }

+ if (idx < (sizeof(gDsiTxIpDivInfo) / sizeof(Dsitx_DphyRangeData)))

+ {

+ dsiObj->dphyTxIpDiv = gDsiTxIpDivInfo[idx].progVal;

+ }

+ else

+ {

+ retVal = FVID2_EFAIL;

+ }

+ }

+

+ /* Calculate DPHY opdiv - PLL output divider */

+ if (retVal == FVID2_SOK)

+ {

+ for (idx = 0U ;

+ idx < (sizeof(gDsiTxOpDivInfo) / sizeof(Dsitx_DphyRangeData));

+ idx++)

+ {

+ min = gDsiTxOpDivInfo[idx].rangeMin * 1000;

+ max = gDsiTxOpDivInfo[idx].rangeMax * 1000;

+ if ((dsiPrms->laneSpeedInKbps >= min) &&

+ (dsiPrms->laneSpeedInKbps <= max))

+ {

+ break;

+ }

+ }

+ if (idx < (sizeof(gDsiTxOpDivInfo) / sizeof(Dsitx_DphyRangeData)))

+ {

+ dsiObj->dphyTxOpDiv = gDsiTxOpDivInfo[idx].progVal;

+ }

+ else

+ {

+ retVal = FVID2_EFAIL;

+ }

+ }

+

+ /* Calculate DPHY fbdiv - PLL feedback divider */

+ if (retVal == FVID2_SOK)

+ {

+ tempResult = (((uint64_t)dsiPrms->laneSpeedInKbps) *

+ ((uint64_t)2U) *

+ ((uint64_t)dsiObj->dphyTxIpDiv) *

+ ((uint64_t)dsiObj->dphyTxOpDiv));

+ tempResult /= (uint64_t)refClkKHz;

+

+ dsiObj->dphyTxFbDiv = (uint32_t)tempResult;

+ }

+ }

+

+ return retVal;

+}

+

static void dssDctrlSetDSIInCtrlMod()

{

/*

diff --git a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/modules/src/app_display_module.c b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/modules/src/app_display_module.c

index d33912b0c..1deae7f73 100644

--- a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/modules/src/app_display_module.c

+++ b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/modules/src/app_display_module.c

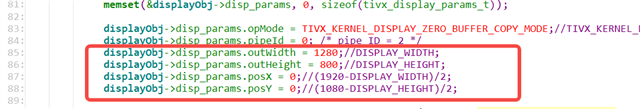

@@ -82,10 +82,10 @@ vx_status app_init_display(vx_context context, DisplayObj *displayObj, char *obj

displayObj->disp_params.opMode = TIVX_KERNEL_DISPLAY_ZERO_BUFFER_COPY_MODE;//TIVX_KERNEL_DISPLAY_BUFFER_COPY_MODE;

displayObj->disp_params.pipeId = 0; /* pipe ID = 2 */

- displayObj->disp_params.outWidth = DISPLAY_WIDTH;

- displayObj->disp_params.outHeight = DISPLAY_HEIGHT;

- displayObj->disp_params.posX = (1920-DISPLAY_WIDTH)/2;

- displayObj->disp_params.posY = (1080-DISPLAY_HEIGHT)/2;

+ displayObj->disp_params.outWidth = 1920U;/DISPLAY_WIDTH;

+ displayObj->disp_params.outHeight = 1080U;//DISPLAY_HEIGHT;

+ displayObj->disp_params.posX = 0;//(1920-DISPLAY_WIDTH)/2;

+ displayObj->disp_params.posY = 0;//(1080-DISPLAY_HEIGHT)/2;

displayObj->disp_params_obj = vxCreateUserDataObject(context, "tivx_display_params_t", sizeof(tivx_display_params_t), &displayObj->disp_params);

status = vxGetStatus((vx_reference)displayObj->disp_params_obj);

diff --git a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/platform/j721e/rtos/common/app_cfg_mcu2_0.h b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/platform/j721e/rtos/common/app_cfg_mcu2_0.h

index 9c5e5f2a6..433b04153 100755

--- a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/platform/j721e/rtos/common/app_cfg_mcu2_0.h

+++ b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/platform/j721e/rtos/common/app_cfg_mcu2_0.h

@@ -88,13 +88,13 @@

/* define below to enable eDP display,

make sure to undef ENABLE_DSS_HDMI & ENABLE_DSS_DSI as well */

- #define ENABLE_DSS_EDP

+ #undef ENABLE_DSS_EDP

/* define below to enable HDMI display,

make sure to undef ENABLE_DSS_EDP & ENABLE_DSS_DSI as well */

#undef ENABLE_DSS_HDMI

/* define below to enable DSI display, make sure to undef ENABLE_DSS_HDMI

& ENABLE_DSS_EDP as well */

- #undef ENABLE_DSS_DSI

+ #define ENABLE_DSS_DSI

#define ENABLE_I2C

#define ENABLE_BOARD

diff --git a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/platform/j721e/rtos/common/app_init.c b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/platform/j721e/rtos/common/app_init.c

index 94709bfe7..083ffef49 100755

--- a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/platform/j721e/rtos/common/app_init.c

+++ b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/platform/j721e/rtos/common/app_init.c

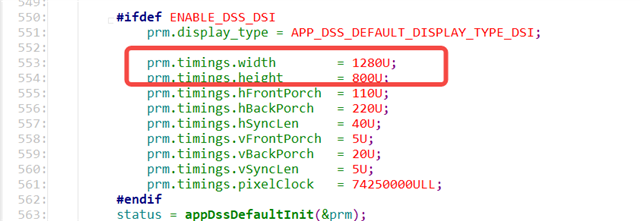

@@ -550,15 +550,15 @@ int32_t appInit()

#ifdef ENABLE_DSS_DSI

prm.display_type = APP_DSS_DEFAULT_DISPLAY_TYPE_DSI;

- prm.timings.width = 1280U;

- prm.timings.height = 800U;

+ prm.timings.width = 1920U;//1280U;

+ prm.timings.height = 1080U;//800U;

prm.timings.hFrontPorch = 110U;

prm.timings.hBackPorch = 220U;

prm.timings.hSyncLen = 40U;

prm.timings.vFrontPorch = 5U;

prm.timings.vBackPorch = 20U;

prm.timings.vSyncLen = 5U;

- prm.timings.pixelClock = 74250000ULL;

+ prm.timings.pixelClock = 143040000ULL;//74250000ULL;

#endif

status = appDssDefaultInit(&prm);

APP_ASSERT_SUCCESS(status);

diff --git a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/utils/dss/src/app_dss_defaults.c b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/utils/dss/src/app_dss_defaults.c

index ddfda3a91..2864f0524 100755

--- a/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/utils/dss/src/app_dss_defaults.c

+++ b/ti-processor-sdk-rtos-j721e-evm-08_01_00_13/vision_apps/utils/dss/src/app_dss_defaults.c

@@ -148,7 +148,7 @@ int32_t appDssDefaultInit(app_dss_default_prm_t *prm)

if (prm->display_type == APP_DSS_DEFAULT_DISPLAY_TYPE_DSI)

{

- appDssConfigureUB941AndUB925(prm);

+// appDssConfigureUB941AndUB925(prm);

}

appDssInitParamsInit(&dssParams);

@@ -348,7 +348,7 @@ int32_t appDctrlDefaultInit(app_dss_default_obj_t *obj)

if(obj->initPrm.display_type==APP_DSS_DEFAULT_DISPLAY_TYPE_DSI)

{

/* Only two lanes output supported for AOU LCD */

- dsiParams.num_lanes = 2u;

+ dsiParams.num_lanes = 4u;//2u;

retVal+= appRemoteServiceRun(cpuId, APP_DCTRL_REMOTE_SERVICE_NAME, APP_DCTRL_CMD_SET_DSI_PARAMS, &dsiParams, sizeof(app_dctrl_dsi_params_t), 0U);

}

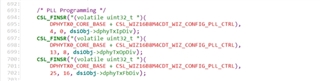

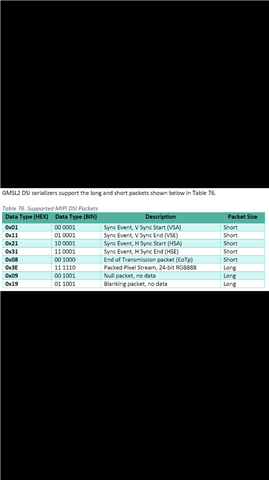

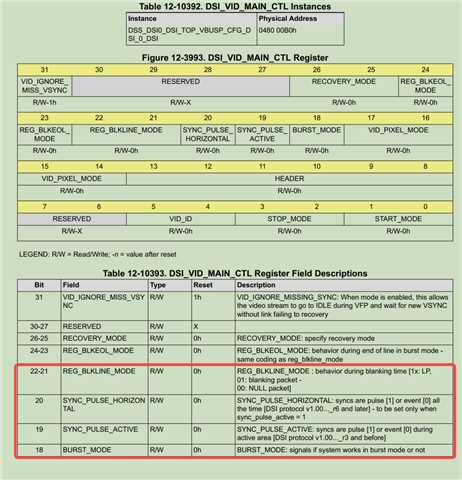

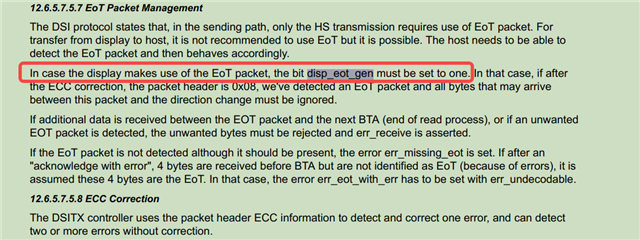

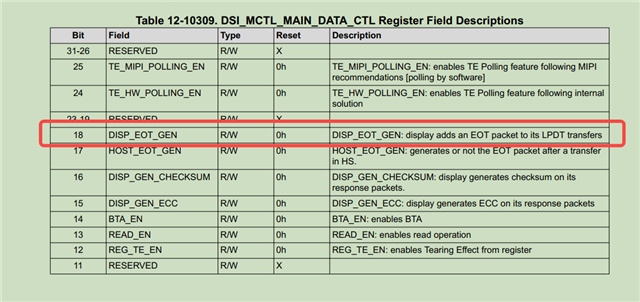

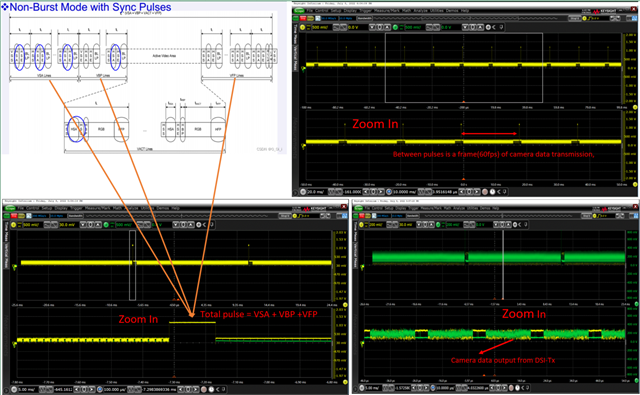

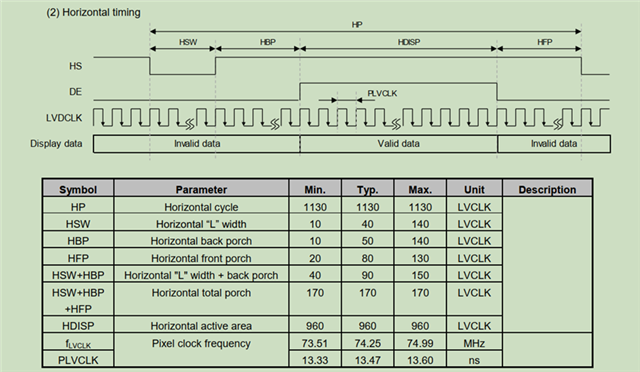

DSI used 4-lane, Since the serializer(Max lane-rate 2.5G/lane) can self-adapt the lane-rate, we use the default dphyTxOpDiv = 02 <1.24 Gbps - 630 Mbps>.

formular:

1. 1920 * 1080 * 60 * 3 * 8 * 1.2 / 4 = 895.795 Mbps/lane

-> dphyTxRate = (0xE << 0) | (0xE << 5)>;//0x1CE

2. dphyTxFbDiv = ((Lane-Rate * 2 * OpDiv * IpDiv) / (19.2MHz))

-> 895.795 * 2 * 2 * 2 / 19.2 = 375

dsiObj->dphyTxIpDiv = 0x2;

dsiObj->dphyTxOpDiv = 0x2;

dsiObj->dphyTxFbDiv = 0x177;//0x178

dsiObj->dphyTxRate = 0x1CE;

dsiObj->cfgDsiTx.numOfLanes = 0x4u;//0x2u;

dsiObj->privDsiTx.numOfLanes = 0x4u;//0x2u

Check whether the above parameters are correctly set ?

Is there any code(s) also need to be modified ?

Please help me to solve this for 1-step.

Best Regards

Murphy.