Other Parts Discussed in Thread: TPS65910,

Hi,

I have questions about AM335x Linux u-boot and configuration of TPS65910 VDDx_REG bit[5](ILMAX).

In u-boot source code(board.c) of TI AM335x Linux SDK, there are configurations of TPS65910 via I2C.

But there are no configuration of TPS65910 VDDx_REG register bit[5](ILMAX).

Does user need to add code which setup the TPS65910 VDDx_REG register value [ILMAX] in the u-boot usually or not?

When [ILMAX] is set to '0', the maximum load current of TPS65910 VDDx will be 1.0[A],

and when set to 1, the maximum load current of VDD2 will be 1.5[A].

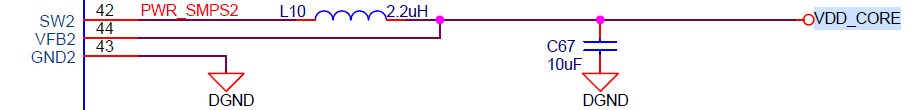

If VDD2(TPS65910) are connected to VDD_CORE(AM3356) which maximum current is 400mA,

should I add the code of setting the ILMAX to 0(max 1.0[A]) to the u-boot?

best regards,

g.f.