Hi,

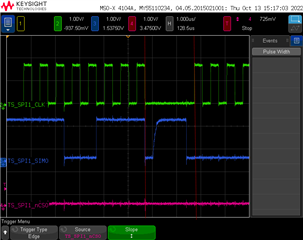

We use MCSPI3_CLK and MCSPI3_SIMO of AM3715 for FPGA upload firmware.

(MCSPI3_SOMI and MCSPI3_CSx didn't be applied and data only be transferred from AM3715 to FPGA)

During data transfer, we found MCSPI3_SIMO seem not be output anymore once enter idle mode (clock stop).

It seem be Hi-Z and be raised to half voltage ~0.8V by FPGA internal pull-up (~40 kΩ).

Does this symptom be correct behavior? Can we adjust some setting or code to make MCSPI3_SIMO continuously be output (either H or L) as idle mode to solve half voltage symptom?

BR,

Yume