Other Parts Discussed in Thread: TMS320LC548

Hello TI,

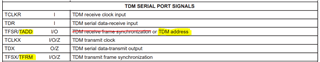

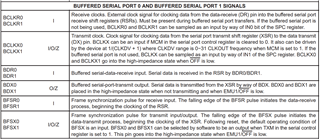

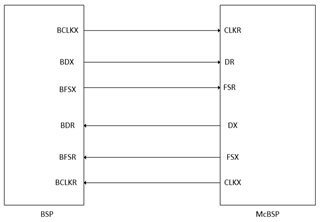

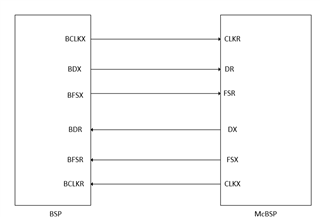

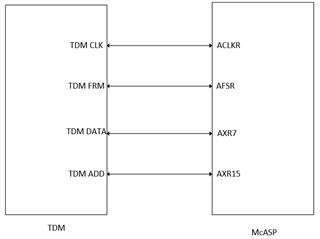

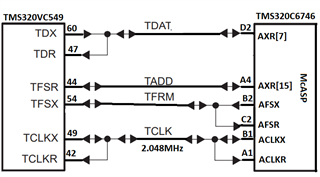

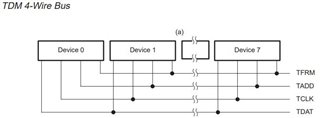

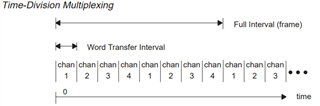

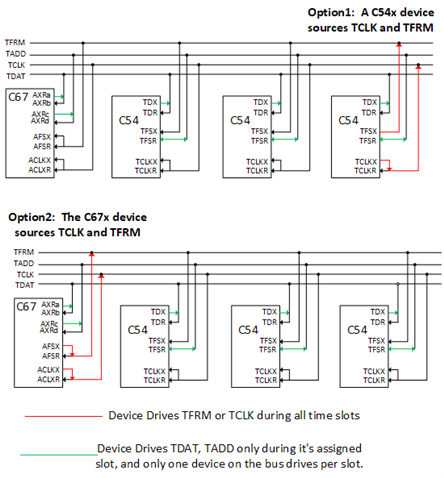

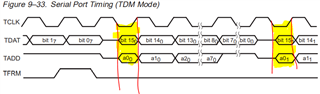

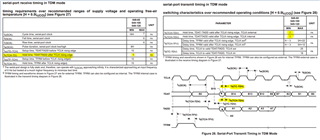

We are looking for a processor with 1TDM interface and 2 Buffered serial ports, and this part: TMS320C6746 DSP has 2McBSP ports and 1McASP port, which states that McBSP/McASP ports supports TDM interface.

So, could you please confirm how we can use this McBSP/McASP ports as TDM and as a Buffered serial ports?

Thanks,

Rajesh..